The AMD Threadripper 2990WX 32-Core and 2950X 16-Core Review

by Dr. Ian Cutress on August 13, 2018 9:00 AM ESTCore to Core to Core: Design Trade Offs

AMD’s approach to these big processors is to take a small repeating unit, such as the 4-core complex or 8-core silicon die (which has two complexes on it), and put several on a package to get the required number of cores and threads. The upside of this is that there are a lot of replicated units, such as memory channels and PCIe lanes. The downside is how cores and memory have to talk to each other.

In a standard monolithic (single) silicon design, each core is on an internal interconnect to the memory controller and can hop out to main memory with a low latency. The speed between the cores and the memory controller is usually low, and the routing mechanism (a ring or a mesh) can determine bandwidth or latency or scalability, and the final performance is usually a trade-off.

In a multiple silicon design, where each die has access to specific memory locally but also has access to other memory via a jump, we then come across a non-uniform memory architecture, known in the business as a NUMA design. Performance can be limited by this abnormal memory delay, and software has to be ‘NUMA-aware’ in order to maximize both the latency and the bandwidth. The extra jumps between silicon and memory controllers also burn some power.

We saw this before with the first generation Threadripper: having two active silicon dies on the package meant that there was a hop if the data required was in the memory attached to the other silicon. With the second generation Threadripper, it gets a lot more complex.

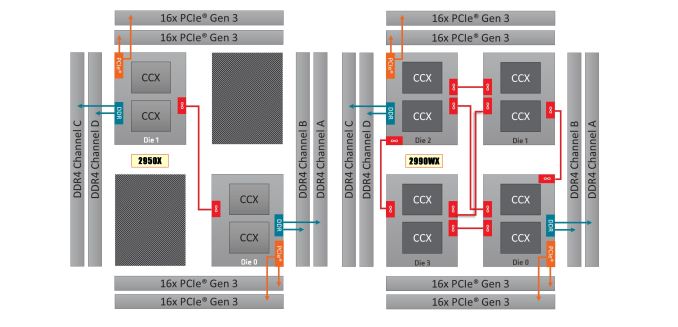

On the left is the 1950X/2950X design, with two active silicon dies. Each die has direct access to 32 PCIe lanes and two memory channels each, which when combined gives 60/64 PCIe lanes and four memory channels. The cores that have direct access to the memory/PCIe connected to the die are faster than going off-die.

For the 2990WX and 2970WX, the two ‘inactive’ dies are now enabled, but do not have extra access to memory or PCIe. For these cores, there is no ‘local’ memory or connectivity: every access to main memory requires an extra hop. There is also extra die-to-die interconnects using AMD’s Infinity Fabric (IF), which consumes power.

The reason that these extra cores do not have direct access is down to the platform: the TR4 platform for the Threadripper processors is set at quad-channel memory and 60 PCIe lanes. If the other two dies had their memory and PCIe enabled, it would require new motherboards and memory arrangements.

Users might ask, well can we not change it so each silicon die has one memory channel, and one set of 16 PCIe lanes? The answer is that yes, this change could occur. However the platform is somewhat locked in how the pins and traces are managed on the socket and motherboards. The firmware is expecting two memory channels per die, and also for electrical and power reasons, the current motherboards on the market are not set up in this way. This is going to be an important point when get into the performance in the review, so keep this in mind.

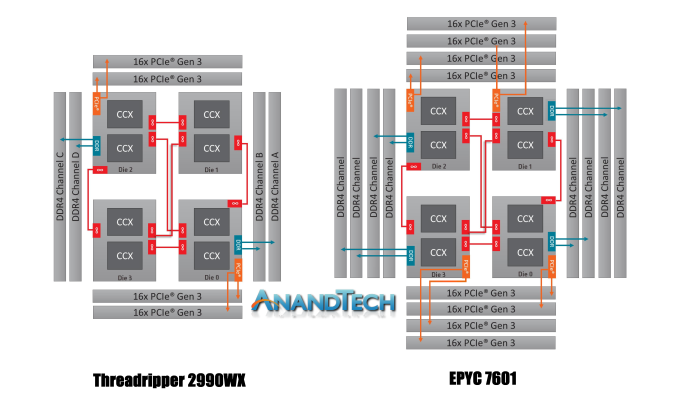

It is worth noting that this new second generation of Threadripper and AMD’s server platform, EPYC, are cousins. They are both built from the same package layout and socket, but EPYC has all the memory channels (eight) and all the PCIe lanes (128) enabled:

Where Threadripper 2 falls down on having some cores without direct access to memory, EPYC has direct memory available everywhere. This has the downside of requiring more power, but it offers a more homogenous core-to-core traffic layout.

Going back to Threadripper 2, it is important to understand how the chip is going to be loaded. We confirmed this with AMD, but for the most part the scheduler will load up the cores that are directly attached to memory first, before using the other cores. What happens is that each core has a priority weighting, based on performance, thermals, and power – the ones closest to memory get a higher priority, however as those fill up, the cores nearby get demoted due to thermal inefficiencies. This means that while the CPU will likely fill up the cores close to memory first, it will not be a simple case of filling up all of those cores first – the system may get to 12-14 cores loaded before going out to the two new bits of silicon.

171 Comments

View All Comments

sjoukew - Thursday, August 16, 2018 - link

There is also an article which shows the difference in performance on windows vs linux for the Threadripper processors. It is amazing to see. https://www.phoronix.com/scan.php?page=article&...ishould - Monday, August 13, 2018 - link

TLDR; Unless you have a very specific need for 32 cores/2990WX, the 2950x is faster and cheaper than the former, even during tasks that traditionally scale well with cores. This is looking to be a good differentiator between Zen+ EPYC and 2990WX. Definitely looking forward to Zen+ EPYC tests!Silma - Monday, August 13, 2018 - link

"... it makes perfect sense for a narrow set of workloads where it toasts the competition."Can you please list those workloads?

When would it make sense to purchase a Threadripper PC vs many 'normal processors' PCs for tasks that you can easily handle in parallel?

Aephe - Monday, August 13, 2018 - link

For example people like me who use their computers for 3D rendering for one. (again: those Corona scores!) The more cores (and Ghz) + ram, the better!jospoortvliet - Saturday, August 18, 2018 - link

And linux/Unix use, like C++ or Rust developer. Or heavy vm user. https://www.phoronix.com/scan.php?page=article&...beggerking@yahoo.com - Monday, August 13, 2018 - link

I'm so glad the competition is back! its been stagnant for years now (at about 4 cores) with Intel dominating the market. For home labs/servers, this is great news! more cores for less without having to go the Xeon ES routes. :)j1ceasar@yahoo.com - Monday, August 13, 2018 - link

Can some one tell me who needs these, i don't as a normal consumercheshirster - Monday, August 13, 2018 - link

"tell me who needs these"As a normal customer you don't need to know this.

Gothmoth - Monday, August 13, 2018 - link

sorry but this handbrake numbers look wrong. no other website i have visited has seen such big differences.twtech - Monday, August 13, 2018 - link

I really would like to see some code compile benchmarks. Next to rendering and other graphic content related tasks, compiling code in large codebases is probably the 2nd most common use-case someone would consider buying a processor like this for, and it seems like there is a dearth of coverage for it.