Cadence & Micron DDR5 Update: 16 Gb Chips on Track for 2019

by Anton Shilov on October 17, 2018 10:15 AM EST

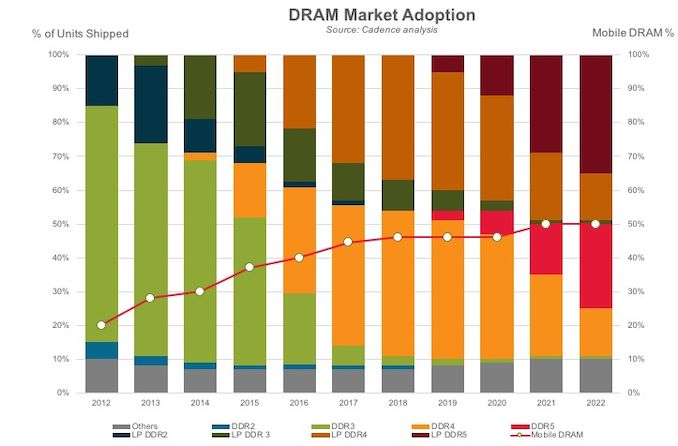

Earlier this year Cadence and Micron performed the industry’s first public demonstration of next-generation DDR5 memory. At a TSMC event earlier this month the two companies provided some updates concerning development of the new memory technology. As it appears, the spec has not been finalized at JEDEC yet, but Micron still expects to start production of DDR5 memory chips in late 2019.

As noted back in May, the primary feature of DDR5 SDRAM is capacity of chips, not just a higher performance and a lower power consumption. DDR5 is expected to bring in I/O speeds of 4266 to 6400 MT/s, with a supply voltage drop to 1.1 V and an allowable fluctuation range of 3% (i.e., at ±0.033V). It is also expected to use two independent 32/40-bit channels per module (without/or with ECC). Furthermore, DDR5 will have an improved command bus efficiency (because the channels will have their own 7-bit Address (Add)/Command (Cmd) buses), better refresh schemes, and an increased bank group for additional performance. In fact, Cadence goes as far as saying that improved functionality of DDR5 will enable a 36% higher real-world bandwidth when compared to DDR4 even at 3200 MT/s (this claim will have to be put to a test) and once 4800 MT/s speed kicks in, the actual bandwidth will be 87% higher when compared to DDR4-3200. In the meantime, one of the most important features of DDR5 will be monolithic chip density beyond 16 Gb.

Leading DRAM makers already have monolithic DDR4 chips featuring a 16 Gb capacity, but those devices cannot offer extreme clocks or I/O speeds because of laws of physics. Therefore, companies like Micron have a lot of work to do in a bid to bring together high DRAM densities and performance in the DDR5 era. In particular, Micron is concerned about variable retention time, and other atomic level occurrences, once production technologies used for DRAM reach 10 – 12 nm. Meanwhile, the DDR5 Add/Cmd bus already features on-die termination to make signals cleaner and to improve stability at high data rates. Furthermore, high-end DDR5 DIMMs will have their own voltage regulators and PMICs. Long story short, while the DDR5 standard is tailored to wed performance and densities, there is still a lot of magic to be done by DRAM manufacturers.

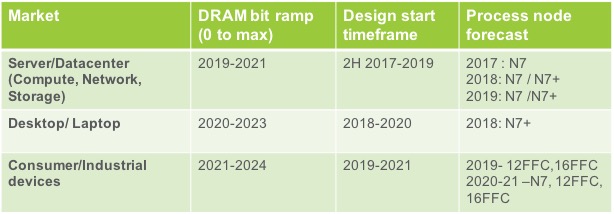

Micron expects to start production of 16 Gb DDR5 chips using its “sub-18nm” fabrication process late in 2019, though this does not necessarily mean that actual applications featuring this memory will be available by the end of next year. Cadence already has DDR5 IP (controller + PHY) implemented using TSMC’s N7 (7 nm DUV) and N7+ (7 nm DUV+EUV) process technologies, so chip developers have what they need to design SoCs compatible with the new type of memory. Cadence is working on DDR5 IP for more advanced process technologies.

Given the key advantages of DDR5, it is not surprising that Cadence forecasts servers to be the first applications to use the new type of DRAM. What is particularly interesting is that Cadence believes that client SoCs made using N7+ process will support DDR5, which essentially means chips due to hit the market in 2020. Given rather quick ramp of DDR5 production predicted by Cadence, it looks like the new DRAM will be supported by a wide range of chips.

Related Reading:

- Cadence and Micron Demo DDR5-4400 IMC and Memory, Due in 2019

- JEDEC: DDR5 to Double Bandwidth Over DDR4, NVDIMM-P Specification Due Next Year

- Micron, Rambus, & Others Team Up To Spur GDDR6 Adoption in Non-GPU Products

- Samsung Updates on GDDR6 Portfolio: 8 Gb and 16 Gb at Multiple Speeds

- Samsung Starts Mass Production of 16Gb GDDR6 Memory ICs with 18 Gbps I/O Speed

- GDDR5X Standard Finalized by JEDEC: New Graphics Memory up to 14 Gbps

- JEDEC Publishes HBM2 Specification as Samsung Begins Mass Production of Chips

Source: Cadence

18 Comments

View All Comments

JoeyJoJo123 - Wednesday, October 17, 2018 - link

I agree. We had one fool that was posting in the comments about wanting extreme speed memory + overclocking it further... For database/software development workloads. And just did not understand that for these workloads memory latency isn't a real bottleneck, completely discounted going with an HEDT platform processor (even though you have more cache, cores, DRAM slots, and other professional features like ECC support, extended AVX instruction support, etc.) and wanted to stick with a 9900k + high capacity+speed RAM.Somethings~something~fool~and~money~departed~something...

No skin off my back. Marketing teams are obviously working their magic on the uninformed.

CaedenV - Wednesday, October 17, 2018 - link

Kinda curious what the workload is where RAM latency is a major issue these days. I mean, it mostly affects things like multi-user databases where you have several calls to RAM at once. No games or desktop software is going to see any major performance gains on reduced latency. Typically the MHz increases more than the CAS, so you end up with (very slightly) lower latency, but massive increase in throughput.The main thing to keep in mind is that DDR5 is focused on the data center where latency is very important. If their massive data sets and thousands of users hitting their servers are not a latency issue, then I am sure that my desktop will be fine lol. More importantly, if latency was a major issue for these people where latency is a main concern, then it would be reflected in the new standards.

Latency use to be a big concern back in the DDR and DDR2 days... DDR3 and beyond there are much bigger fish to fry.

limitedaccess - Wednesday, October 17, 2018 - link

Gaming benefits heavily from lower latency (as in real latency, not just lower timings), particularly with regards to worse case scenarios (min fps, 99th percentile fps metrics) if trying to drive higher fps (high refresh displays) in non GPU limited scenarios.boeush - Thursday, October 18, 2018 - link

For consumers, latency (as well as power, bandwidth, and compactness) might be better addressed with HBM. I expect by 2021+ we'll be on HBM3 or HBM4 or something. You get better latency simply by virtue of shorter traces between memory cells and the CPU/caches - and also by more parallelism (when you have lots of concurrent requests from multiple cores/threads, this gets to be important.) Yes, you get lower maximum capacity with HBM than what's possible with DRAM, but for most consumer workloads that's not really a huge issue - particularly given the HBM capacity roadmaps. The only real issue is price - but on that account, DRAM hasn't been doing itself any favors, lately...Valantar - Wednesday, October 17, 2018 - link

Looking forward to seeing what can be done for APUs with this. Seems like AMD planned (very!) well when they said AM4 would last until 2020.ToTTenTranz - Wednesday, October 17, 2018 - link

Except they didn't plan Raven Ridge very well, given the lack of LPDDR support which put them out of the race for the ever expanding 2-in-1 detachable tablet market (i.e. Surface Pro, Lenovo Miix, Envy X2, etc.).Hopefully Picasso will support LPDDR4x or even LPDDR5. Fingers crossed.

Amandtec - Wednesday, October 17, 2018 - link

2020 + 5nm chips + DDR4 + QLC flash = good time to buy an APU that doesn't suck.boozed - Thursday, October 18, 2018 - link

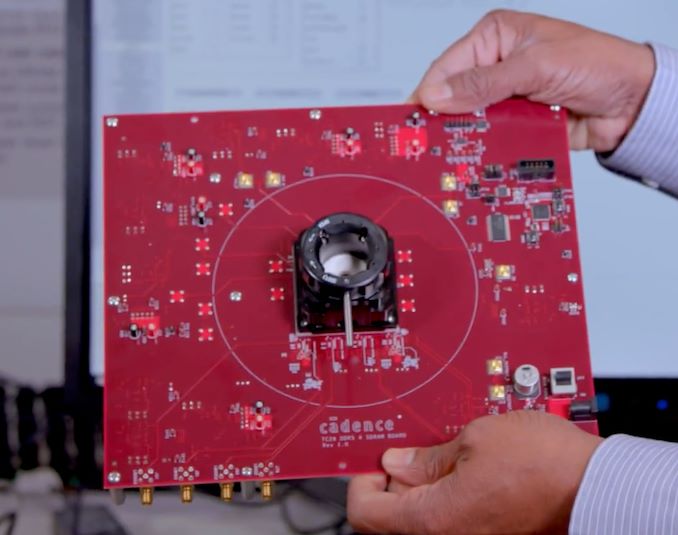

So those two photos of a red circuit board simply entitled "DDR5 board" but which carry no explanation or caption. What is it?