Intel's Architecture Day 2018: The Future of Core, Intel GPUs, 10nm, and Hybrid x86

by Dr. Ian Cutress on December 12, 2018 9:00 AM EST- Posted in

- CPUs

- Memory

- Intel

- GPUs

- DRAM

- Architecture

- Microarchitecture

- Xe

Intel’s First Fovoros and First Hybrid x86 CPU: Core plus Atom in 7 W on 10 nm

Perhaps someone will correct me, but I can’t ever remember a time when Intel has put multiple x86 cores of different configurations on the same bit of silicon (ed: Intel Edison). Ever since Arm starting doing it with its big.Little designs in smartphones, a perennial question was if Intel was going to do something similar, either with big and small Atom cores, or by moving a high-performance Core into the mix. When Intel left the smartphone and tablet market, we assumed the idea was dead. But, like a reanimated zombie, it has risen from the grave. Enter Intel’s Hybrid x86 CPU.

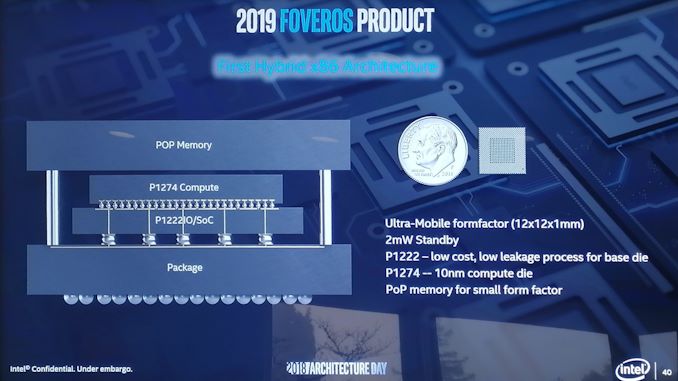

This tiny 12x12 package is built using Intel’s Fovoros technology, using a 22FFL IO chip as the active interposer connected with TSVs to a 10nm die that contains both a single Sunny Cove core and four Atom (Tremont?) cores. This tiny chip is smaller than a dime, and is designed to have a 2 mW standby power. It would appear that this chip is destined for mobile devices.

Here’s the manufacturing diagram, showing the idea that POP memory is placed over the Fovoros design to give the final product. Very much like a mobile chip.

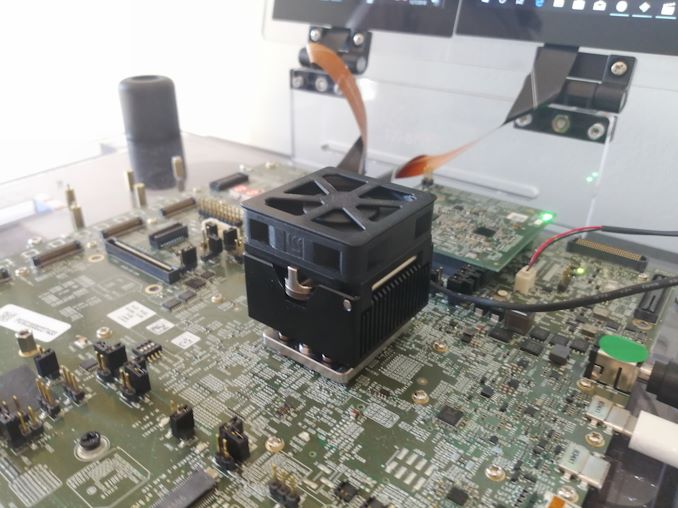

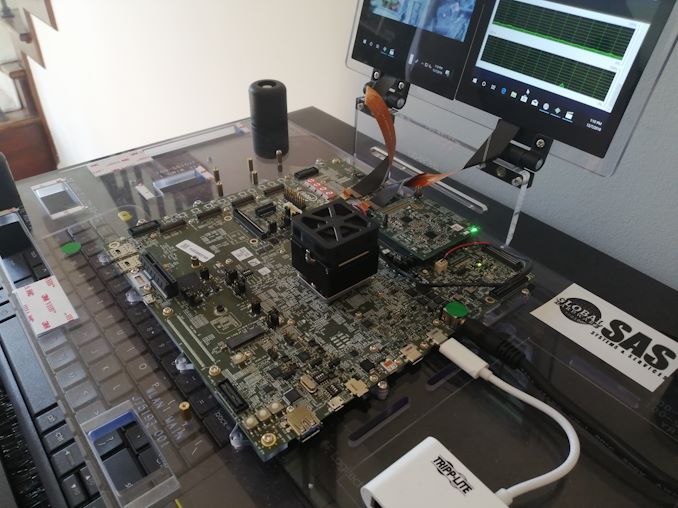

The demo system that Intel had on display looked similar to the previous Sunny Cove design, however this heatsink was smaller and it had a few different connectors. We were told that this chip will support PCIe for M.2 as well as UFS, both of which are found in mobile. There also looked like a couple of SIM card connectors on this motherboard.

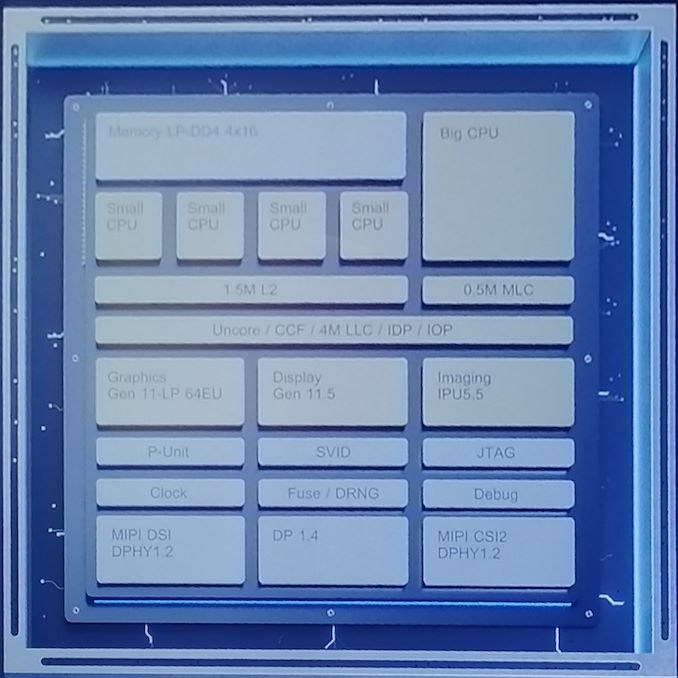

The key part of this discussion however is this block diagram that was on one of the Intel slides. Here we see a single ‘Big CPU’ with 0.5 MB of private medium level cache, four ‘Small CPU’s with a shared 1.5 MB L2 cache, an uncore that has 4MB of last level cache, a quad-channel memory controller (4x16-bit) with support for LPDDR4, a 64 EU design with Gen11 graphics, the Gen 11.5 display controller, a new IPU, MIPI support with DisplayPort 1.4, and all of this in a tiny package.

Seriously though, this has the potential to be a large revenue stream for Intel. They’ve made this chip, which allows the cores to enter C6 sleep states when not in use, that has a die size smaller than 12x12mm (144 mm2), and target the sub-7W fanless device market. That’s with a big Core, four Atom cores, and a GT2 64 EU design.

Intel actually says that the reason why this product came about is because a customer asked for a product of about this performance but with a 2 mW standby power state. In order to do this, Intel created and enhanced a number of technologies inside the company. The final product is apparently ideal for the customer, however the chip will also be made available for other OEMs.

In our Q&A session with the senior members of Intel, it was clear that this technology is still in its infancy, and Intel now has a new toy to play with. Jim Keller stated that internally they are trying lots of new things with this technology to see what works and what would make a good product, so we should be seeing more Foveros designs through 2019 and 2020.

148 Comments

View All Comments

johannesburgel - Wednesday, December 12, 2018 - link

"We have a new method inside the company to decouple IP from the process technology. You must remember that customers buy the product, not a transistor family. It’s the same transformation AMD had to go through to change the design methodology when they were struggling."...doesn't that basically mean they're going fabless, or are at least going to develop a design for multiple processes so they can also use other fabs as well? Not that I'm disagreeing with that! If I was Intel I would have started doing so years ago, when everybody else was starting to do it.

anonomouse - Wednesday, December 12, 2018 - link

I think this just means fewer hand placed/routed custom logic blocks, and more synthesis/APR. If you look at most other dies these days, you see a sea of gates. When you look at intel dies, in the cpu cores you see very tight, regular logic blocks. Every mention of "abstraction" in the Q&A screamed synthesis/APR. This may make it possible for them to port to other foundries if they wanted to, but I doubt they would.An interesting question is whether this has any implications to power/timing/area optimization vs. the current approach, as a lot of their ability to push very high clocks might come from how much more custom logic design goes into their implementation.

kapg - Wednesday, December 12, 2018 - link

I guess in the image Intel 'CPU Core Roadmap' for Atom the name 'Next' Month is a typo from IntelAlexvrb - Wednesday, December 12, 2018 - link

"quad-channel memory controller (4x16-bit)"Well, we know the GPU won't be competitive with upcoming ARM designs, then. Otherwise, very neat mobile class chip design.

Arbie - Wednesday, December 12, 2018 - link

"Golden Cove ... is firmly in that 2021 segment ... we’re likely to see it on 10nm and or 7nm."Likely? If it isn't one of those two it will be big news indeed.

HStewart - Thursday, December 13, 2018 - link

10nm is already stated for Sunny Cove in 2019, so it likely 7nm - but keep in mind the process (nm) is decouple for process - so it could be 10nm or 7nmajc9988 - Wednesday, December 12, 2018 - link

Ian, the active interposer isn't new, and I am wanting o know more exactly what has been moved to the active interposer. AMD's whitepapers on the topic, using routers, etc., on an active interposer, was published in 2014 and a follow up on 2015. In late 2017, AMD published a white paper dealing with the costs of doing so, where producing an active interposer on smaller than 40nm resulted in costs being the same as producing a monolithic die. AdoredTV did two videos on this topic months ago, as a matter of fact. So, unless they are sticking some of the features that AMD put on the I/O die onto the active interposer, this is doing what AMD plans to do but chose not to on the basis of cost. Check out these papers and videos:http://www.eecg.toronto.edu/~enright/micro14-inter... http://www.eecg.toronto.edu/~enright/Kannan_MICRO4... https://youtu.be/G3kGSbWFig4 https://seal.ece.ucsb.edu/sites/seal.ece.ucsb.edu/... https://www.youtube.com/watch?v=d3RVwLa3EmM&t=...

Intel seems to now be using ideas from everywhere else in the industry, while also using 22nm fabs that would have been slated for decommission if not for the 10nm fiasco that is their process, which they had to push certain chipsets to due to the 14nm shortage, meaning they need to keep the fab time full to justify them keeping the lights on and a 22nm active interposer fits the bill. The article practically writes itself.

iwod - Thursday, December 13, 2018 - link

No news on opening up TB3? Which they promised to do in 2018.The Hybrid, I wish it had two HP Core. but 7W is actually the same TDP for MacBook Air Retina.

The_Assimilator - Thursday, December 13, 2018 - link

Thunderbolt is dead in mainstream PCs at this point, because there's no use-case in which it outperforms USB by enough to justify its cost (both of implementation and in the peripherals that people actually want to use). It's become another almost-Mac-exclusive like Firewire, and will share the same fate.gamerk2 - Thursday, December 13, 2018 - link

Yep, this pretty much the same thing that happened to Firewire. Thunderbolt never had a reason to exist; USB3 handles pretty much every TB3 use-case.