Intel’s Comet Lake U&Y 495 Chipset Datasheet: x8 Link, USB 3.2 Gen 2 Support

by Anton Shilov on September 23, 2019 12:30 PM EST- Posted in

- Chipsets

- Intel

- Motherboards

- Ice Lake

- Comet Lake

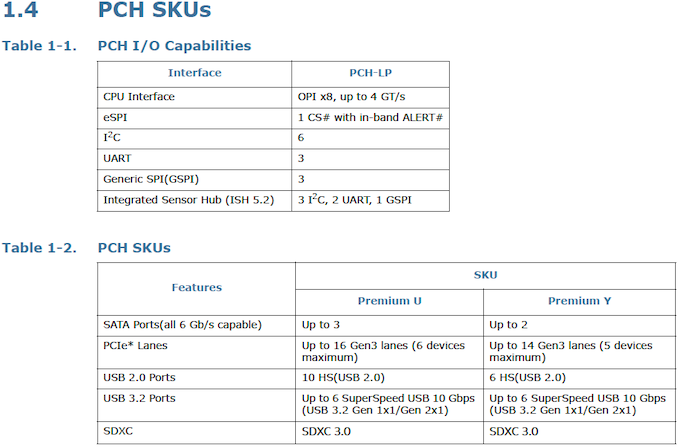

Intel has published datasheet of its upcoming Intel 495-series chipsets revealing their key features. As it turns out, the family will feature two chipsets aimed at different types of premium laptops, one for Y series and one for U series.

Intel’s 495 chipsets will be compatible with ‘Premium-U’ and ‘Premium-Y’ processors featuring an OPI x8 interface with up to 4 GT/s data transfer rate. Intel’s 495-series PCH will also support up to 16 PCIe 3.0 lanes, up to three Serial ATA ports, up to six USB 3.2 Gen 2 ports (10 Gbps), up to 10 USB 2.0 connectors, an integrated GbE MAC, a built-in Wi-Fi MAC that requires a CNVi module, and all the other familiar features of Intel’s modern chipsets (e.g., RST, AMR, TXT, VT, etc.).

Intel does not disclose in its document codenames of CPUs to be supported by its 495 chipsets, but it is likely that the new PCH will support the company’s latest 10th Generation Core processors known as Ice Lake and Comet Lake. Meanwhile, it remains to be seen which Intel’s chipsets support the manufacturer’s upcoming desktop CPUs.

Related Reading:

- Intel Documents Show Driver Support for Unannounced 400-Series Chipsets

- Intel Adds B365 Chipset to Lineup: The Return of 22nm

- Cypress and Zhaoxin Have USB 3.1 Gen 2 USB Controllers

Source: Intel

44 Comments

View All Comments

danielfranklin - Monday, September 23, 2019 - link

Is the link from the CPU to the PCH doubled in bandwidth? Or am i reading it wrong?The bandwidth starved link would be a huge upgrade if they can do that.

Everything gets attached to the PCH in the consumer desktop and mobile systems and the 4x link is just a joke these days.

Honestly one of the best things AMD did with their new platform was simply add 4 lanes to the CPU dedicated for a PCI-E SSD, no longer having to share it with every other device in the system.

Of course this doesnt apply if you arent using a dedicated GPU, but its hard to even find an H series laptop that doesnt give all its PCI-e bandwidth to a GPU im not using (thanks to Optimus and its other amazing laggy mess via the on-die graphics)

DanNeely - Monday, September 23, 2019 - link

I wondered the same as well, but no. OPI x8 has the same bandwidth as DMI x4, and has been used for the last few generations of intels low power combined CPU/southbridge packages. Apparently over a few mm distance 8 lanes of PCIe 2 consumes less power than 4 lanes of PCIe 3.edzieba - Tuesday, September 24, 2019 - link

OPI 3.0 can operate at PCIe 2.0 or 3.0 signalling rates, but usually operates at 2.0 to reduce power consumption. An x8 wide link at 2.0 would match the bandwidth of OPI x4 at 3.0 rates, but consume less power.at8750 - Tuesday, September 24, 2019 - link

Ice Lake-U/Y with 495 series chipset(IceLake PCH)Comet Lake-U/Y with 400 series chipset(CometLake PCH)