AMD Details Renoir: The Ryzen Mobile 4000 Series 7nm APU Uncovered

by Dr. Ian Cutress on March 16, 2020 11:00 AM ESTPower and Battery Life

Earlier in the year AMD was keen to promote that in Renoir it has made significant advances as to how power is managed across the APU, leading to increased performance and better battery life. The two key figures here were ‘20% reduced SoC power’ and ‘5x reduction in power gating latency’ (also known as an 80% reduction, because you can’t have a 5x reduction of a time). We now have some details.

First up it should be mentioned that 7nm helps a lot here. The smaller process node, with smaller transistors (assuming they’ve been laid out correctly), will require a lower voltage. That lower voltage directly translates into lower power, and we’ve seen how well AMD has pushed the 7nm designs on the desktop and in the enterprise space to know that compared to previous process nodes, there is a lot of power to save here. That being said, the design choices and features matter too.

AMD’s power management all goes through a system-level management controller. For this generation, AMD has re-written the firmware with speed in mind (they claim 33% faster), but also made other improvements, such as aggressive clock gating of the L3 cache when not needed, and using power optimized circuits for IO features such as for the embedded display controller and PCIe physical layers.

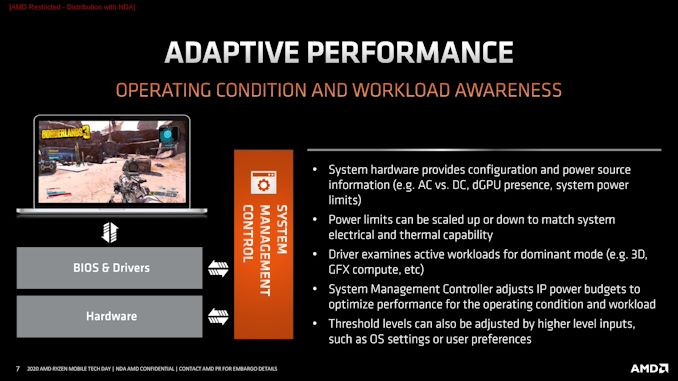

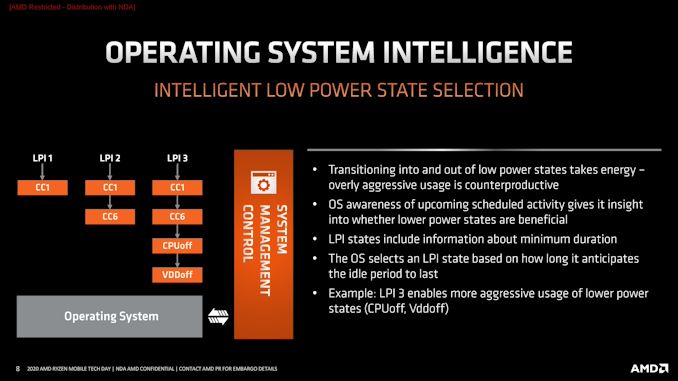

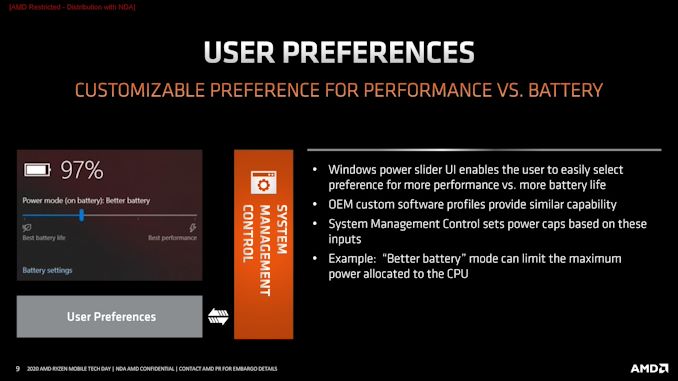

The updated system management controller (SMC) is built around user preference. In this case if the user tells the OS he or she wants more performance, or more battery life, then the SMC can take into consideration everything involved in the system and plan accordingly. If the OS can provide guidance as to an upcoming workload, then voltages and frequencies (or parts of the chip unused can be put in idle), then the SMC is built to understand it.

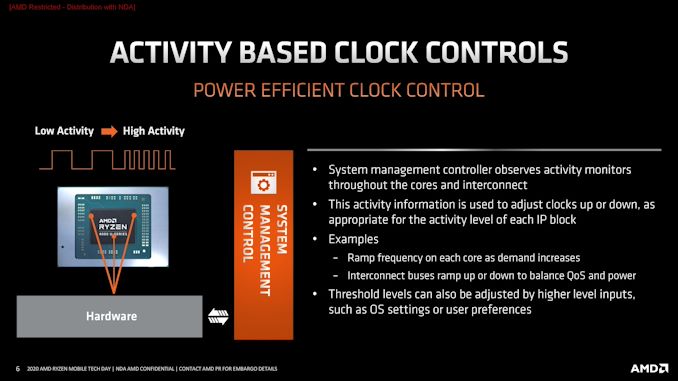

Ultimately there are many sensors around the APU, monitoring activity and the type of activity going on in that particular region, even down to the types of instructions being used. The SoC is a lot more dynamic in its clock control, allowing for different clock domains in various parts of the SoC to be adjusted depending on both the activity of the region but also the thermal limits, system limits, and other items that might affect performance. This is especially useful for powering down parts of the SoC that are not in use, leading to AMD’s efficiency claims, or the performance claims such as maintaining a specific bandwidth across an interconnect (quality of service). The thresholds for these activity monitors can be set by the OS and by the user. The SMU also takes into account the power source (battery vs power supply) and connected hardware (displays, power over USB).

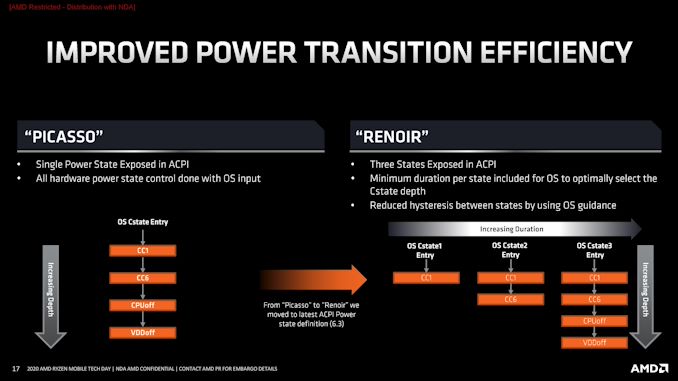

For the power gating latency, AMD has doubled the save and restore bus width from the buffers to the cores, allowing for a system to resume faster from a CPUOFF state. Not only this, but AMD is using the ACPI 6.3 specifications to take advantage of offering multiple C states in the OS.

One of the issues of the previous generation of Picasso APUs, on the left, is that there was only a single set of states that the processor could be in. This means that at any time, the CPU could fall from a power state (a P state) into a lower power state, or an idle state, or an off state. If the CPU went too far down this stack, while it would be saving power, each hop down the rabbit hole meant a longer time to get back out of it, diminishing performance and latency but also requiring more power changes at the silicon level. Each hop in its own right requires additional power.

With the new Renoir designs, a system can take advantage of multiple different sets of states. This means that the CPU can’t go down too low when the system is in use. With a system in use, the OS or system controller can’t put parts of the core into low power states because those are not available, which means that even if the system goes into the lowest power mode possible, while the system is still being used, then there are fewer jumps to get back up to high speed.

As the system becomes less used, known as ‘increased idle duration’, then the system has access to sets of states that allow the parts of the APU to enter deeper idle states. This means that the system can only enter a low frequency domain if that part of the core has been sufficiently idle, or user interaction has willed it.

This is all part of the ACPI 6.3 standard, and AMD states that this combined with the reduced SoC power gives both better battery life and better immediate performance for the user. To show this in action, AMD pinpointed a common activity that most users might be familiar with: opening applications.

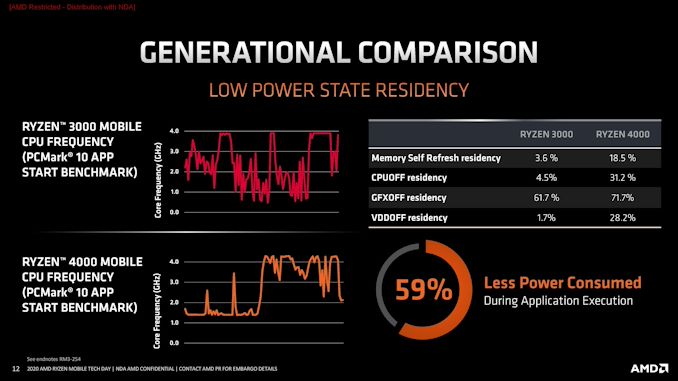

In this case, AMD took the start of the PCMark 10 Application Loading benchmark. In this benchmark a number of applications are loaded, and the requirements are often more IO driven than CPU driven. A good CPU with a fast reaction time will keep its power and frequency low while the IO requests are being done, and speed up one or two threads when the CPU needs to get involved.

In AMD’s benchmark, where they are using frequency as a proxy for power, They show that in the initial 5 seconds of the test, the new Ryzen 4000 CPU is hovering at an idle frequency, whereas the older Ryzen 3000 CPU is fluttering around, even peaking near 4.0 GHz when it doesn’t need to. This allows parts of the new CPU to be powered down for longer periods of time, even when the system is actually in use.

When I asked AMD’s executives where they stand on battery life, one of them hinted that the difference between themselves and the competition (in similar designs) should be on the order of minutes rather than dozens of minutes. Specifically AMD sees itself better than the competition in productivity/web browsing workloads, graphics workloads, and video playback, and cited that most battery benchmarks don’t often take into account a good mix of ‘the average user’. A number of the media responded that often our benchmarks are geared towards different types of users consummate to our audience, such as gamers or content creators. Ultimately we will see what the results are when we have hardware on hand.

95 Comments

View All Comments

watzupken - Tuesday, March 17, 2020 - link

To this point,"Renoir has a huge range of load vs. power consumption: Please, please, PLEASE ensure that in all form factors users can make a choice of power consumption vs. battery life or cooling by setting max and sustained Wattage preferably at run-time and not hard-wiring this into distinct SKUs. I’d want a 15 Watt ultrabook to sustain a 35 Watt workload screaming its head off, just like I’d like a 90 Watt desktop or a 60 Watt NUC to calm down to 45/35/25 Watt sustained for night-long batches in the living room or bed-side—if that’s what suits my needs: It’s not a matter of technology, just a matter of ‘product placement’."

I doubt they will ever let you do that on a laptop or even NUC officially. The cooling solution implemented is usually very closely correlated to the TDP of the processor. Even when it is a downgrade from say a 45W to 35W, these are usually tightly controlled by AMD and Intel. There is no guarantee that all chips will work well at a certain clockspeed across various TDP. For example, a Ryzen 7 4800H may not be able to run at a 4800U speed when you reduce the TDP from 45W to 15W. U series chips are binned to be able to run at that the specific clockspeed and likely also commands a higher premium.

Tams80 - Tuesday, March 17, 2020 - link

This. If you want to push your system, with the risk of damaging it, then you should be free to as long as there's no direct risk of it causing harm.Namisecond - Thursday, March 26, 2020 - link

Why are you using a laptop for a workstation task? If you have to hide it in a closet, then you really don't get to choose the where and when. Might as well rent out some hardware at a data center and do the work remotely. Not judging, just saying your way of doing things doesn't make a whole lot of sense to me.yankeeDDL - Tuesday, March 17, 2020 - link

I have a question: let's take Ryzen 7 4800U and Ryzen 3 4300U devices.Both are 15W parts, yet, one has 4/4 C/T and the other 8/16.

The 4300U has less GPU CU and lower clock.

How can they have the same TDP? Does this mean that the 4300U is likely to stay at Turbo a lot more consistently than the 4800U?

Spunjji - Tuesday, March 17, 2020 - link

Possibly. It will more likely mean (at least initially) that the 4300U is an inferior specimen and needs more voltage to reach its standard clock speeds.yankeeDDL - Tuesday, March 17, 2020 - link

It's possible. I guess also that's why they can increase the base clock on lower core count.djayjp - Tuesday, March 17, 2020 - link

AMD: "Making the best graphics engine even better -- Vega 7nm" Surely they mean Navi...? Confused.yankeeDDL - Tuesday, March 17, 2020 - link

No, it is Vega architecture, ported to 7nm. With some improvements (as described in the article itself), but it is still Vega.djayjp - Wednesday, March 18, 2020 - link

Right I get that but surely Navi is a better architecture than Vega (look at Radeon VII vs 5700 XT).djayjp - Wednesday, March 18, 2020 - link

Especially for mobile