Hot Chips 2020 Live Blog: Intel's Tiger Lake Mobile CPU (12:30pm PT)

by Dr. Ian Cutress on August 17, 2020 3:30 PM EST- Posted in

- CPUs

- Intel

- Mobile

- Notebooks

- Live Blog

- 15W

- Tiger Lake

- Hot Chips 32

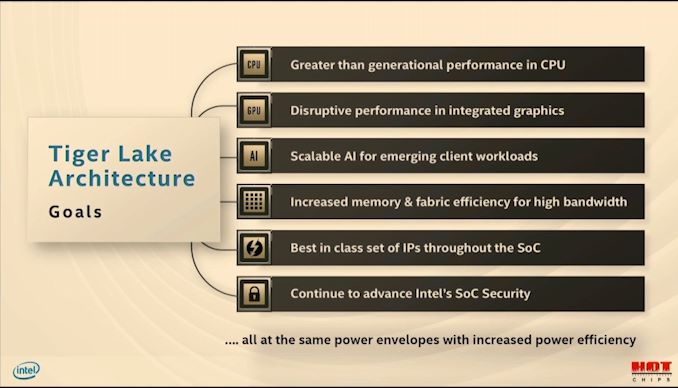

03:31PM EDT - Tiger Lake - generational improvement for graphics and CPU

03:31PM EDT - From 9W to 65W

03:32PM EDT - New AI features for new workloads

03:32PM EDT - USB4, PCIe4, TB4

03:32PM EDT - Increased power efficiency

03:33PM EDT - More cache, more performance, better efficiency, more headroom, more features

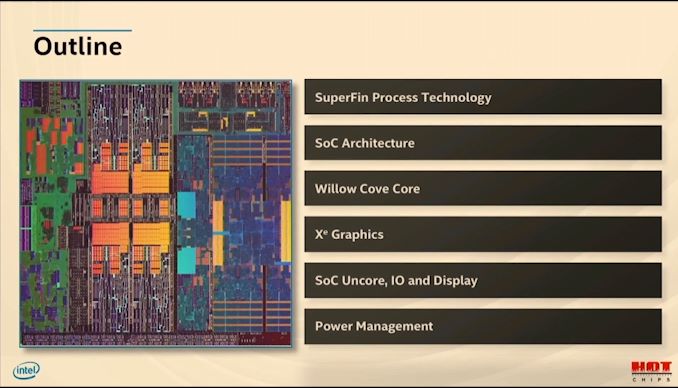

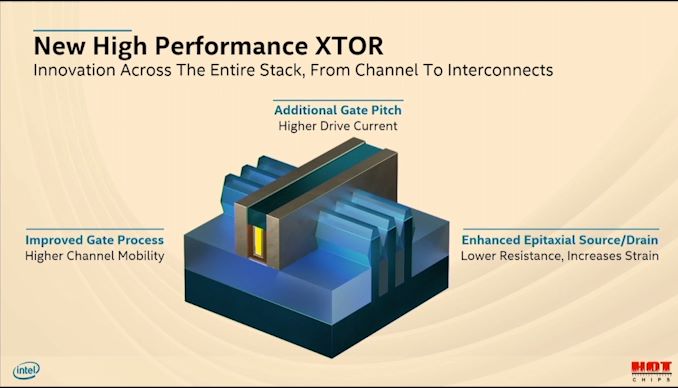

03:34PM EDT - New process technology

03:34PM EDT - new transistor

03:34PM EDT - SuperFin

03:35PM EDT - optimized non-perf critical IPs for the new transistor to allow for more headroom for the perf-critical stuff

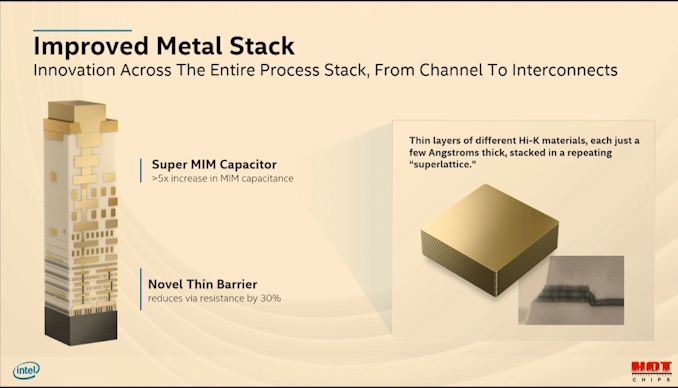

03:35PM EDT - Improved Metal Stack

03:35PM EDT - To new high perf layers at the top

03:36PM EDT - New SuperMIM

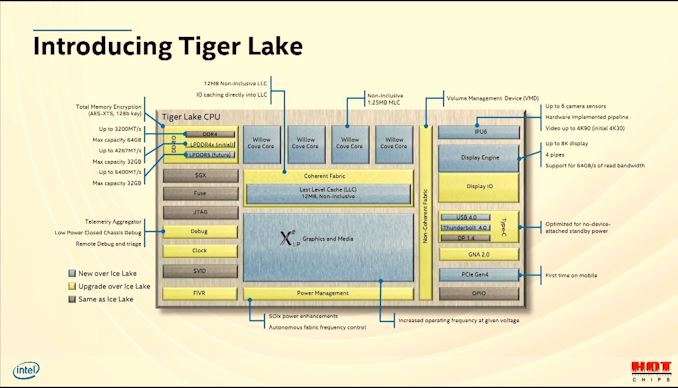

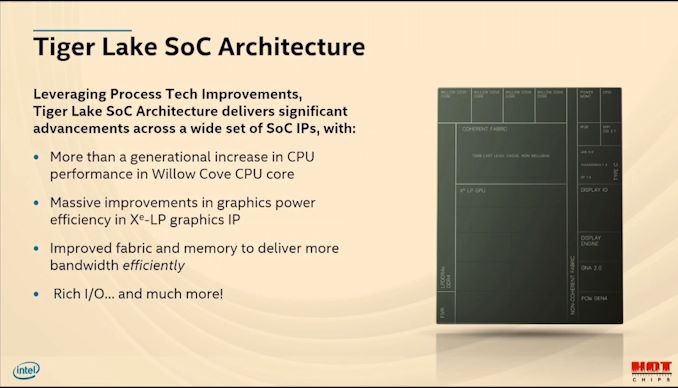

03:36PM EDT - Here's the high level diagram

03:36PM EDT - Different power envelopes might have different amount of cores

03:36PM EDT - (which means 8 core is coming later at 65 W)

03:37PM EDT - Four Willow cove cores, 96 EUs of Xe graphics

03:37PM EDT - LPDDR5-5400 support, PCIe 4.0 x4

03:37PM EDT - 12 MB non-inclusive L3

03:37PM EDT - 1.25 MB non-inclusive L2

03:37PM EDT - 4x4K display pipes

03:38PM EDT - IPU6 - two different flavors based on the chip config (?!?)

03:38PM EDT - Improved Debug

03:39PM EDT - GNA 2.0 does up to 38 GigaOPs, 1 GOP per watt (and it scales)

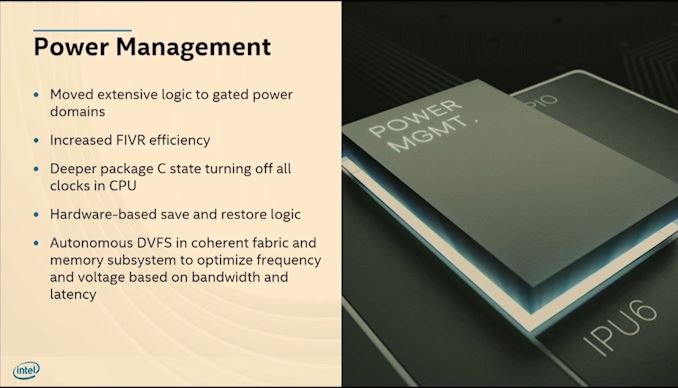

03:40PM EDT - Better FIVR

03:41PM EDT - Total Memory Encyption support

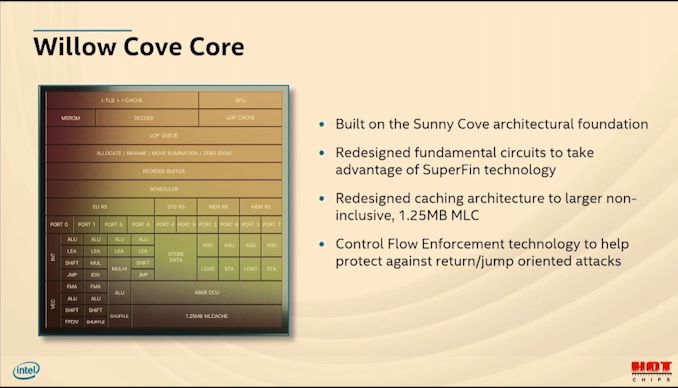

03:41PM EDT - Willow Cove in Tiger Lake

03:41PM EDT - Built on Sunny Cove base

03:42PM EDT - Had three options - IPC, improve circuits on freq for SuperFin, or a mix

03:42PM EDT - The second was used - focus on frequency

03:42PM EDT - Also cache adjustments and security

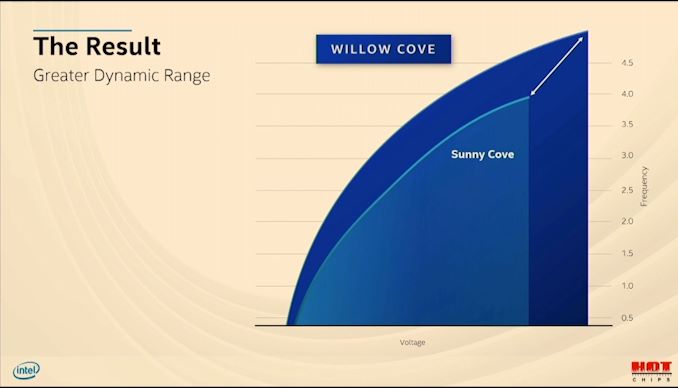

03:43PM EDT - Willow Cove has a better dynamic range - better perf/watt at all points and much higher voltage/freq

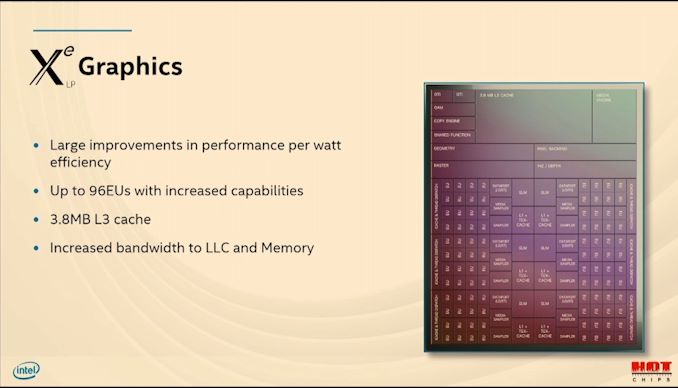

03:44PM EDT - Now to 96 EUs

03:44PM EDT - More info on Xe later

03:45PM EDT - Increased bandwidth

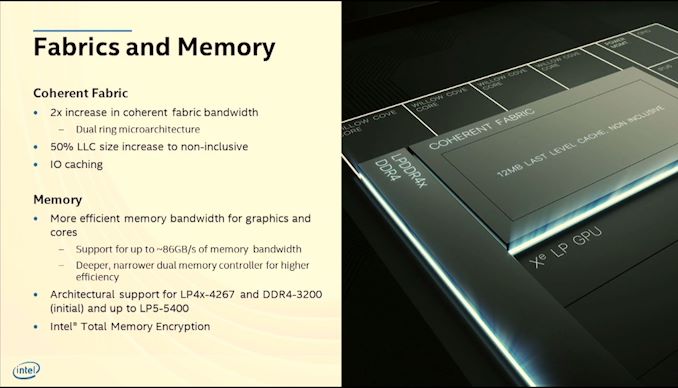

03:45PM EDT - Dual ring architecture

03:45PM EDT - IO caching

03:46PM EDT - Up to 86 GB/s on DRAM

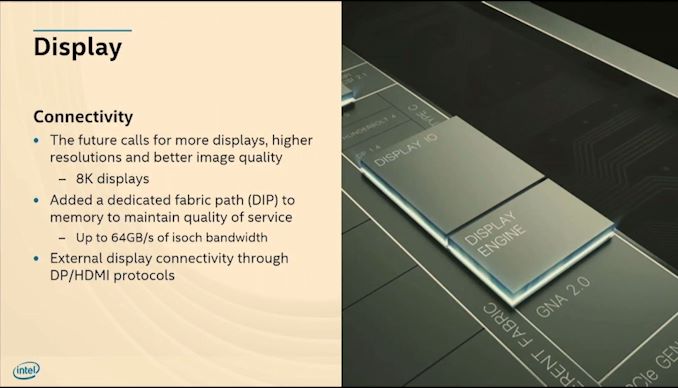

03:47PM EDT - Increased display support - but depends on memory configurations. Added dedicated fabric path to memory, up to 64 GB/s

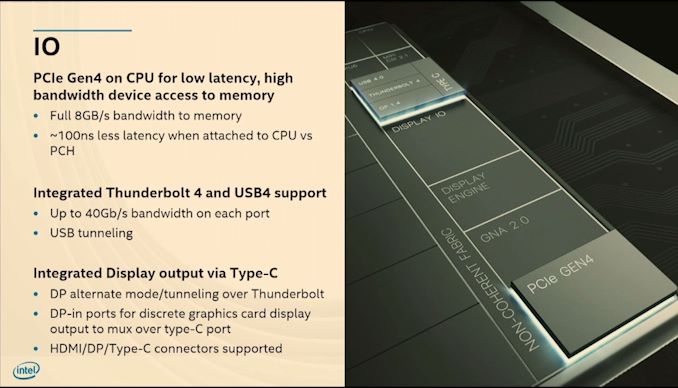

03:48PM EDT - PCIe 4.0 at 8 GB/s

03:48PM EDT - 100ns less latency for CPU attach compared to PCH attach

03:48PM EDT - Integrated TB4 and USB4, full compliance

03:48PM EDT - Display via Type-C using DP tunneling over TB

03:50PM EDT - Overall better power management for better idle power and quicker entry/exit

03:50PM EDT - DVFS on fabric

03:52PM EDT - More than a generational improvement in a single product cycle

03:53PM EDT - Q&A time

03:54PM EDT - Q: Only 4 CPU cores? What's the range? A: Will depend on the SKU config, announced in product launch in September.

03:54PM EDT - Q: Additional latency for TME? A: No disclosing.

03:54PM EDT - Q: Perf impact of TME? A: See the product launch at Sep 2

03:55PM EDT - Q: BW of TME? A: No loss of BW

03:55PM EDT - Q: PL2? A: See Sep 2 product launch.

03:56PM EDT - Q: Is incoming PCIe traffic cached in LLC? A:You can.

03:56PM EDT - Q: What sort of frequency is DVFS? A: No hard numbers. We sample the utilization and we can offer a fine granularity. (so once per hour?)

03:57PM EDT - Q: L2 latency with increased cache size? A: No answer.

03:58PM EDT - Client have always used L3 is inclusive - we now use non-inclusive. Once you grow that L2 cache to 1.25 MB, making L3 inclusive would consume 5 MB.

03:59PM EDT - Now there's an hour break for lunch, before Raja's keynote. Come back then!

41 Comments

View All Comments

ikjadoon - Monday, August 17, 2020 - link

Super MIM was discussed last week...this is nothing new, besides the Q&A at the bottom.tipoo - Monday, August 17, 2020 - link

TSMC is buying the same ASML machines that helped create SuperFin, so it would be funny if they called it UberFin or something just to be spitefulMeteor2 - Thursday, August 20, 2020 - link

LolCajunArson - Monday, August 17, 2020 - link

I frankly wasn't very impressed by the forum moderator who continually asked questions that are either well-known information (Tiger Lake launches with up to 4 cores with 8 core variants coming later but he kept asking questions on that regard) or that he knew the Intel guys would not answer like cache latency numbers.I would have preferred some more intelligent questions about the design philosophies behind the various functional units, which might be something that they could answer since it wouldn't be divulging an exact architectural number that's still under NDA.

alufan - Monday, August 17, 2020 - link

I thnk the one thing that every ones ignoring is the Console chips AMD has some serious fire power tucked into those little boxes just makes you wonder if they will ever release something similar for Desktop use or what do they have tucked away for launch later.drothgery - Monday, August 17, 2020 - link

No one's ignoring them, but they're never going to make sense for a desktop. The CPU's nothing special (same as the Ryzen 4xxx APUs but clocked relatively low, so nice, but you can already get better performance from both AMD and Intel desktop chips), and the GPUs are bigger and better than anyone using an integrated GPU on a desktop would ever need. And the console-specific stuff for using GDDR6 main memory and the like isn't useful for a PC.ilkhan - Monday, August 17, 2020 - link

OMG liveblog with the updates appearing on the bottom where they should be. Hallelujah!timecop1818 - Monday, August 17, 2020 - link

it's always been this? the *live* portion updates on top, then when the event is over everything is flipped back to normal order.Meteor2 - Thursday, August 20, 2020 - link

YesKimGitz - Monday, August 17, 2020 - link

I'm waiting for Tiger Lake H, I'm hoping for 6-8cores 45-65W variants with LPDDR5 in Q1 2021.