Intel's Process Roadmap to 2025: with 4nm, 3nm, 20A and 18A?!

by Dr. Ian Cutress on July 26, 2021 5:00 PM ESTNew Technology Features for 2024: RibbonFETs

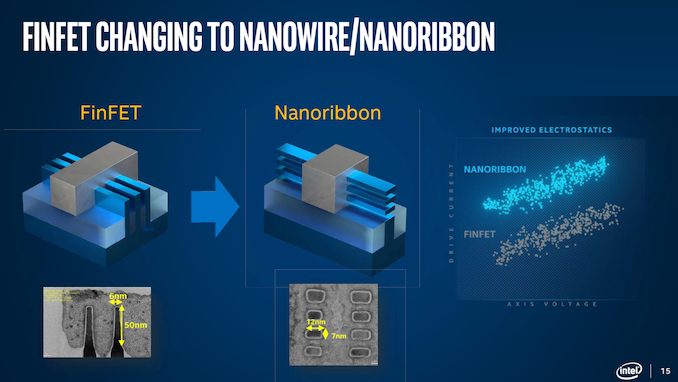

One of the major features of this roadmap is highlighted when it shifts to 20A, Intel’s process name referring to Angstroms rather than nanometers. At this juncture, as mentioned above, Intel will be transitioning from its FinFET design over to a new type of transistor, known as a Gate-All-Around transistor, or GAAFET. In Intel’s case, the marketing name they are giving their version is RibbonFET.

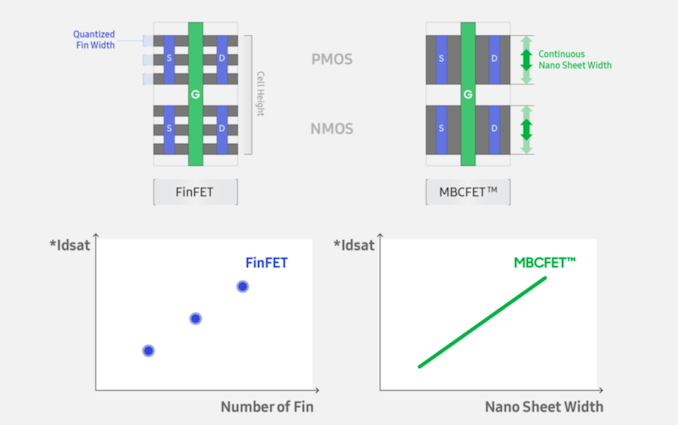

It has been widely expected that once the standard FinFET runs out of steam that the semiconductor manufacturing industry will pivot to GAAFET designs. Each of the leading edge vendors call their implementation something different (RibbonFET, MBCFET), but it is all using the same basic principle – a flexible width transistor with a number of layers helping drive transistor current. Where FinFETs relies on multiple quantized fins for source/drain and a cell height of multiple tracks of fins, GAAFETs enable a single fin of variable length, allowing the current for each individual cell device to be optimized in power, performance, or area.

Intel has been discussing GAAFETs in technical semiconductor conferences for a number of years, at the International VLSI conference in June 2020, then CTO Dr. Mike Mayberry showcased a diagram with the enhanced electrostatics of moving to a GAA design. At the time we asked about Intel’s timescale for implementing GAA in volume, and were told to expect them ‘within 5 years’. At present Intel’s RibbonFET is due to come with the 20A process, likely to be productized by the end of 2024 based on the roadmaps outlined above.

In Intel’s RibbonFET diagrams for this event, they’re showing both PMOS and NMOS devices, as well as what clearly looks like a 4-stack design. Given that I have seen presentations from Intel involving anything from 2-stack to 5-stack at the industry conferences, we confirmed that Intel will indeed be using a 4-stack implementation. The more stacks that are added, the more process node steps are required for manufacturing, and to quote Intel’s Dr. Kelleher, ‘it’s easier to remove a stack than to add one!’. Exactly what is the right number of stacks for any given process or function is still an active area of research, however Intel seems keen on four.

In comparison with Intel’s competitors,

TSMC is expected to transition to GAAFET designs on its 2nm process. At its annual Tech Symposium in August 2020, TSMC confirmed that it would remain on FinFET technology all the way to its 3nm (or N3) process node as it has been able to find significant updates to the technology to allow performance and leakage scaling beyond what was initially expected – N3 is quoted to have up to a 50% performance gain, 30% power reduction, or 1.7x density gain over TSMC N5. Staying on FinFETs, TSMC stated, provides comfort to its customers. Details on TSMC’s N2 have not been disclosed.

Samsung by contrast has stated that it will be introducing its GAA technology with its 3nm process node. Back in Q2 2019, Samsung Foundry announced the first v0.1 development kit of its new 3GAE process node using GAAFETs was being made available to key customers. At the time Samsung predicted volume production by end of 2021, and the latest announcement suggests that while 3GAE will deploy in 2022 internally, main customers may have to wait until 2023 for its more advanced 3GAP process.

To put this into a table:

| Gate-All-Around Transistor Deployment | |||

| AnandTech | Name | Process | Timeframe |

| Intel | RibbonFET | 20A | 2024 |

| 18A | 2025 | ||

| TSMC | GAAFET | N2 / 2nm | EoY 2023? |

| Samsung | MBCFET | 3GAE | 2022 |

| 3GAP | 2023 | ||

By this metric, Samsung might be first to the gate, albeit with an internal node, while TSMC is going to get a lot out of its N5, N4, and N3 nodes first. Around end of year 2023 is when it gets interesting as TSMC may be looking at its N2 designs, while Intel is committed to that 2024 timeframe. The official slide says first half 2024, though as a technology announcement vs product announcement, there is often some lag between the two.

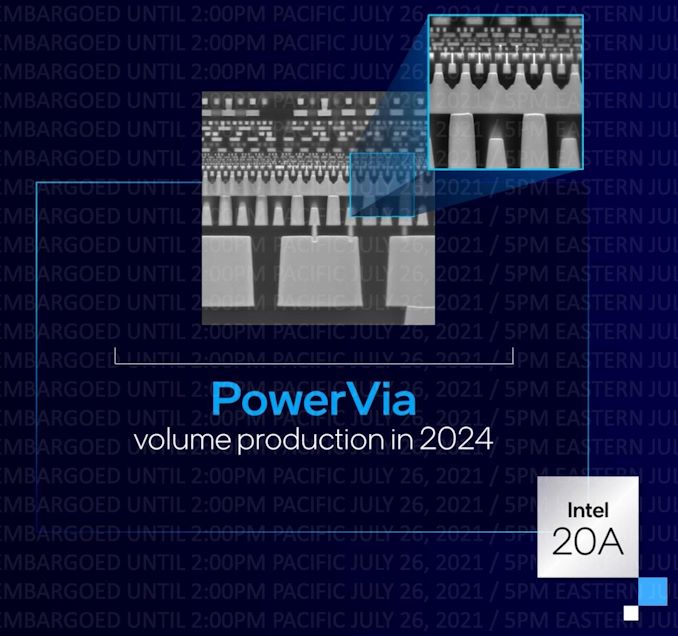

New Technology Features for 2024: PowerVias

The other arm of Intel’s 20A designs in 2024 is what the company is calling ‘PowerVia’. The concept here pivots the traditional understanding of chip design from a multi-layered cake into a sandwich of sorts.

The manufacturing process of a modern circuit starts the transistor layer, M0, as the smallest layer. Above that, additional metal layers are added at increasing sizes to account for all the wiring needed between the transistors and different parts of the processor (cache, buffers, accelerators). A modern high-performance processor typically has anywhere from 10 to 20 metal layers in its design, with the top layer where the external connections are placed. The chip is then flipped over (known as flip chip) so that the chip can talk to the outside world with those connections on the bottom, and the transistors at the top.

With PowerVias, we now put the transistors in the middle of the design. On one side of the transistors we put the communication wires that allow parts of the chip to talk to each other. On the other side are all the power related connections (along with power gating control). In essence, we moved to a sandwich where the transistors are the filling. This is usually referred to as ‘backside power delivery’ in the industry – PowerVia is Intel’s marketing name.

From a holistic level, we can ascertain that the benefits of this design start with simplifying both the power and the connectivity wires. Typically these have to be designed to ensure there is no signaling interference, and one of the big sources of interference are large power carrying wires, so this takes them out of the equation by putting them on the other side of the chip. It also works the other way – the interference of the interconnected data wires can increase the power delivery resistance, resulting in lost energy and thermals. In this way, PowerVias can help new generations of transistors as drive currents increase by having the power directly there, rather than routed around the connectivity.

There are a couple of hurdles here to mention however. Normally we start manufacturing the transistors first because they are the most difficult and most likely to have defects – if a defect is caught early in the metrology (defect detection in manufacturing), then that can be reported as early in the cycle as possible. By having the transistors in the middle, Intel would now be manufacturing several layers of power first before getting to the tough bit. Now technically these layers of power would be super easy compared to the transistors, and nothing is likely to go wrong, but it is something to consider.

The second hurdle to think about is power management and thermal conductivity. Modern chips are built transistor first into a dozen layers ending with power and connections, and then the chip is flipped, so the power hungry transistors are now at the top of the chip and the thermals can be managed. In a sandwich design, that thermal energy is going to go through whatever ends up on the top of the chip, which is most likely going to be the internal communication wires. Assuming that the thermal increase of these wires doesn’t cause any issues in production or regular use, then perhaps this isn’t so much of an issue, however it is something to consider when heat has to be conducted away from the transistors.

It is worth noting that this ‘backside power delivery’ technology has been in development for a number of years. Across five research papers presented at the VLSI symposium in 2021, imec presented several papers on the technology showing recent advancements when using FinFETs, and in 2019 Arm and imec announced similar technology on an Arm Cortex-A53 built on an equivalent 3nm process in imec’s research facilities. Overall the technology reduces the IR drop on the design, which is becoming increasingly harder to achieve on more advanced process node technologies to drive performance. It will be interesting to see the technology when it is in high volume on high performance processors.

326 Comments

View All Comments

Oxford Guy - Wednesday, August 11, 2021 - link

Says the person who said, in reply to one of my posts ‘we know you’re smart ... use your powers for good’.You typically post whatever sounds reasonable at a given time, no matter how inaccurate it is. I, by contrast, am capable of remembering what has been said — the positions that have been taken.

One cannot simultaneously claim I’m obviously intelligent and that my posts are valid. One cannot also post ‘agreed’ — as you did in another topic whilst pretending that my posts are vapid — unless you’re with that very vapidity.

I also find it droll that you employ the royal ‘we’ here. Are you a member of staff or merely that entitled?

Oxford Guy - Wednesday, August 11, 2021 - link

And... please — for the benefit of this forum...Learn the list of common logical fallacies. Your latest use of ad baculum is only worthy of yet another eyeroll.

mode_13h - Thursday, August 12, 2021 - link

> Says the person who said, in reply to one of my posts ‘we know you’re smart> ... use your powers for good’.

There's no logical inconsistency, there. Most of your posts seem to pull threads off-topic and offer little of value to the original subject. And quite a few are just snarky, cynical trolls.

> You typically post whatever sounds reasonable at a given time

I try to engage my brain and look at the other side of an issue, or at least from a perspective other than my narrow self-interest. And most often, what draws me to the other side of an issue is when someone takes an extreme position or makes absolutist statements that seem unjustified. If there's one thing you could say I consistently oppose, it's oversimplification.

> no matter how inaccurate it is.

Ah, now that's interesting. Accuracy is rooted in fact. And the facts are where you completely fall apart. You consistently fail to support your claims and assertions with good & relevant sources.

With that said, if I post something that's demonstrably inaccurate, then please do us *all* a favor and point it out. I never claimed to know everything or be infallible. I've even learned things from debates and spirited discussions.

> I, by contrast, am capable of remembering what has been said —

> the positions that have been taken.

This might blow your mind, but I have actually changed positions, on a few occasions. Not many, but I'm actually willing to re-evaluate my position, after looking at the arguments on both sides.

Also, I try not to be overly partisan, which is to say that I try not to take a side of an issue purely on the basis of political allegiance or preoccupation with self-consistency. If I think one side is overstating their case or otherwise acting in bad faith, I might come out against their position, even while I might've previously been supportive on another issue.

> One cannot simultaneously claim I’m obviously intelligent and that my posts are valid.

Why not? Intelligence describes the actor, while the writing of posts describes their actions. I can criticize the latter, without invalidating the former. Plenty of smart people do things that are thoughtless, counterproductive, antisocial, or worse. However, at some point, the actions do begin to define the actor.

> One cannot also post ‘agreed’ — as you did in another topic whilst pretending

> that my posts are vapid

I said they're "consistently", not "uniformly" or "without exception". If I thought you were a complete waste of time, then I wouldn't spend so much time replying to you.

> unless you’re with that very vapidity.

Well, I'm not going to claim I've never made a vapid post. I try to say things worth saying, but I'm not infallible. It is just a news comment thread, and I don't worry too much about a post here or there.

> I also find it droll that you employ the royal ‘we’ here.

It wasn't. I was speaking on behalf of myself AND other forum participants. That it was preceded by "I think", signifies it as a speculative statement. Others are welcome to disagree.

ikjadoon - Monday, July 26, 2021 - link

What? Intel has long sandbagged its numbers. Unfortunately, we've all decided to follow the marketing, so yeah, at least Intel is more honest now. But none of it matters until they deliver it. I'm not trusting any marketing announcements from Intel. I want the desktop / laptop CPU in-hand so that there's actual benchmarks.//

https://www.tsmc.com/english/dedicatedFoundry/tech...

Otherwise there's no need for the TSMC marketing dept to magically shrink the fake 16nm node to become a fake 12nm.

>An enhanced version of TSMC's 16nm process was introduced in late 2016 called "12nm".

https://en.wikichip.org/wiki/16_nm_lithography_pro...

mode_13h - Monday, July 26, 2021 - link

> at least Intel is more honest now.Wow, that sure takes some mental gymnastics to see Intel participating in the same disinformation race as "more honest".

You could say they're being more consistent... until TSMC and Samsung decide to rebrand their process nodes to stay ahead of Intel's naming.

All of this argues that it's an exercise in futility to pretend these names actually mean anything. They should just use codenames, or maybe a completely arbitrary schema involving sequential numbering + letters or Greek alphabet characters.

ikjadoon - Tuesday, July 27, 2021 - link

Sure, noted. "More honest" relative to the industry = more consistent. I'm flabbergasted how anyone has any problem with this, when literally no one had a problem TSMC & Samsung have done this for years, lol.OK? Why wouldn't TSMC & Samsung play more bullshit w/ foundry marketing? They started it a while ago, so it's more than expected to continue. Good technology has never needed exaggerations: Intel, TSMC, and Samsung all know that.

lol, this is just the tip of the iceberg of marketing. We don't need "i7" or "Ryzen 3", either. How deep do you want to go?

Node names *absolutely* mean something: it's the progression within a foundry. Almost nobody dual-sources CPUs any more, but everyone wants to play "Fantasy Nodes".

That's the more interesting problem. Why is the peak density leap between 10->7 larger than 7->4? Because, clearly, density is not the *only* metric involved in a node.

mode_13h - Wednesday, July 28, 2021 - link

> literally no one had a problem TSMC & Samsung have done this for years, lol.How do you know? Did you run a survey?

Unlike what Intel is doing, Samsung and TSMC never had a press conference to announce they're going to use more dishonest naming. If they had, you'd probably have seen the same kind of sentiment you're seeing when Intel did just that.

> Good technology has never needed exaggerations

That's not true. Not as long as exaggerations can help you sell a little more. Nvidia exgerates like all damn day, even while they've been sitting comfortably atop the heap.

> it's the progression within a foundry

Right, so the names just need to reflect that. Like I said, they should use sequential numbering for big steps, and then letter suffixes to denote minor iterations.

> density is not the *only* metric involved in a node.

All the more reason to cut ties between their naming and any pretense of density.

wut - Thursday, July 29, 2021 - link

"Right, so the names just need to reflect that. Like I said, they should use sequential numbering for big steps, and then letter suffixes to denote minor iterations"Tell TSMC, Samsung, along with everyone else to do it, at the same time.

(TSMC with its N7+, N5P, and Samsung with its 3GAE...)

If you want to apply some standard, apply it to everyone first. Lest you'd be the one who ends up looking agenda-ladened.

mode_13h - Sunday, August 1, 2021 - link

> Tell TSMC, Samsung, along with everyone else to do it, at the same time.The beauty of it is that Intel can simply opt out of the game, without requiring others to do the same.

> If you want to apply some standard

No, you don't have to replace a false standard with another standard (false or not). The point is just to drop the pretense that the node names really mean anything.

twtech - Tuesday, July 27, 2021 - link

A really bold move would have been to move away from "nm" naming altogether and call it 100D or something for 100 million transistor density.