How Low Cost Can Chiplets Go? Depends on the Optimization, says AMD’s CEO Dr. Lisa Su

by Dr. Ian Cutress on January 14, 2022 10:00 AM EST- Posted in

- CPUs

- AMD

- APUs

- Trade Shows

- SoCs

- Lisa Su

- Interviews

- CES 2022

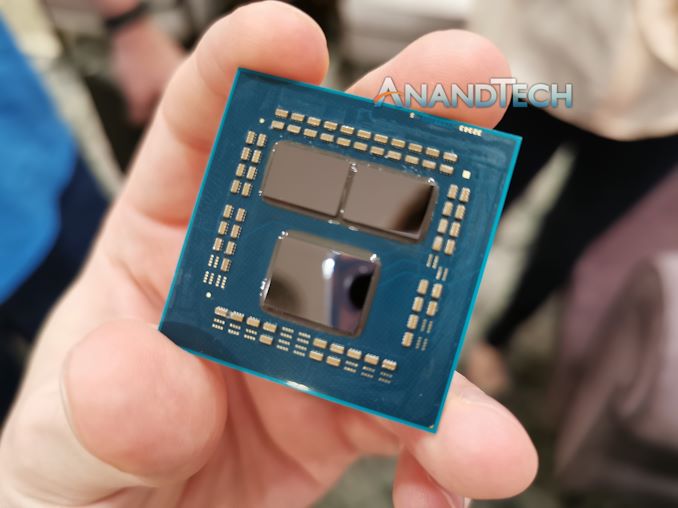

While not the absolute first company in the market to talk about putting different types of silicon inside the same package, AMD’s launch of Ryzen 3000 back in July 2019 was a first in bringing high performance x86 computing through the medium of chiplets. The chiplet paradigm has worked out very well for the company, having high performance cores on optimized TSMC 7nm silicon, while farming the more analog operations to cheaper GlobalFoundries 14nm silicon, and building a high speed interconnect between them. Compared to a monolithic design, AMD ends up using the better process for each feature, smaller chips that afford better yields and binning, and the major cost adder becomes the packaging. But how low cost can these chiplet designs go? I put this question to AMD’s CEO Dr. Lisa Su.

In AMD’s consumer-focused product stack, the only products it ships with chiplets are the high-performance Ryzen 3000 and Ryzen 5000 series processors. These range in price from $199 for the six-core Ryzen 5 3600, up to $799 for the 16-core Ryzen 9 5950X.

Everything else consumer focused is a single piece of silicon, not chiplets. Everything in AMD’s mobile portfolio relies on single pieces of silicon, and they are also migrated into desktop form factors in AMD’s desktop APU strategy. We’re seeing a clear delineation between where chiplets make financial sense, and where they do not. From AMD’s latest generation of processors, the Ryzen 5 5600X is still a $299 cost at retailers.

One of the issues here is that a chiplet design requires additional packaging steps. The silicon from which these processors are made have to sit in a PCB or substrate, and depending on what you want to do with the substrate can influence its cost. Chiplet designs require high speed connections between chiplets, as well as power and communications to the rest of the system. The act of putting the chiplets on a singular substrate also has an effective cost, requiring accuracy - even if 99% accurate placement per chiplet on a substrate means a 3 chiplet product as a 3% yield loss from packaging, raising costs. Beyond this, AMD has to ship its 14nm dies for its products from New York to Asia first, to package them with the TSMC compute dies, before shipping the final product around the world. That might be reduced in future, as AMD is believed to make its next-generation chiplet designs all within Asia.

Ultimately there has to be a tipping point where simply building a monolithic silicon product becomes better for total cost than trying to ship chiplets around and spend lots of money on new packaging techniques. I asked the question to Dr. Lisa Su, acknowledging that AMD doesn’t sell its latest generation below $300, as to whether $300 is the realistic tipping point from the chiplet to the non-chiplet market.

Dr. Su explained how in their product design stages, AMD’s architects look at every possible way of putting chips together. She explained that this means monolithic, chiplet, packaging, process technologies, as the number of potential variables in all of this have direct knock-on effects for supply chain and cost and availability, as well as the end performance of the product. Dr. Su stated quote succinctly that AMD looks for what is best for performance, power, cost – and what you say on the tipping point may be true. That being said, Dr. Su was keen not to directly say this is the norm, detailing that she would expect in the future that the dynamic might change as silicon costs rise, as this changes that optimization point. But it was clear in our discussions that AMD is always looking at the variables, with Dr. Su ending on a happy note that at the right time, you’ll see chiplets at the lower end of the market.

Personally, I think it’s quite telling that the market is very malleable to chiplets right now in the $300+ ecosystem. TSMC D0 yields of N7 (and N5) are reportedly some of the industry best, which means that AMD’s mobile processors in the ~200 sq mm range can roll off the production line and cater for everything up to that $300 value (and perhaps some beyond). Going bigger brings in die size yield constraints, where chiplets make sense. We’re now in at a stage where if Moore’s Law continues, how much compute can we fit in that 200 sq mm sized silicon, and which markets can benefit from it – or are we going to get to a point where so many more features are added that silicon sizes would increase, necessarily pushing everything down the chiplet route. As part of the discussion, Dr. Su mentioned economies of scale when it comes to packaging, so it will be interesting to see how this dynamic shakes out. But for now it seems, AMD’s way to address the sub-$300 market is going to be with either last generation hardware, or monolithic silicon.

This article was updated to clear up some of the language around certainty and conjecture based on rumor.

55 Comments

View All Comments

brantron - Friday, January 14, 2022 - link

1) Zen 3 is larger. TSMC has raised prices several times since 2019. There are OEM only SKUs that presumably cost less.Epyc uses dies with more than 2 cores fused off, at significantly higher prices.

So 5600X ≠ 3600. It's bound to be binned in a specific way, like just the extra leaky dies.

2) Rembrandt is PCIe 4.0. If it's higher volume, it could turn up for desktops sooner. They'll really have to if Zen 4 APUs are delayed.

neblogai - Sunday, January 16, 2022 - link

1.These chiplets are small, so price difference from Zen2 chiplet to Zen3 chiplet can only amount to ~$1, and ~20% price increase- another ~$2.2. No need to bin it in any real special way. It is the 5800X and higher that need better dies. And even if you had to bin- then 5600X being ~6% faster than 12400F in gaming (HU review), AMD could still make a slightly lower locked 'R5 5600', and use low quality dies.

3. Rembrandt is huge (~208mm2), it is DDR5/LPDDR5 only, and has no motherboards- so not fit for budget for a long time still.

msroadkill612 - Friday, January 14, 2022 - link

We have short memories.the rule in this biz has always been that the real meat is in lucrative server/hpc. Viabilty there pays for cutting edge designs that can later filter down to mainstream.

amd ingeniously & of impecunious necessity, came up w/ a single design that could do both - so well in fact, it worked in reverse - desktop paid the bills while high end had a long think about epyc.

a facet of it tho, was they came in very strong for mainsteream - an ~8 core was their ~START point - MEH, it worked very well.

a/ i dont think these cheap intel chips are a patch on a 6 core zen rig, & nor were they cheap til amd forced them to be.

Intel is on borrowed time surviving/relying on this custom - they need very high margins & amd is slowly strangling them.amdS ability to spread the same mass produced, hi yield chiplet around so many products & markets gives them enviable costs. They can sell ~$200 6 cores PROFITABLY any time - but WHY? when folks happily pay more?

Calin - Monday, January 17, 2022 - link

"Viabilty there pays for cutting edge designs that can later filter down to mainstream"Selling in the server / high performance / enthusiast market (and especially holding the performance crown) basically means selling for a higher ASP, average selling price. However, a lot of the income comes from the low end and middle market, where most of the chips are selling.

As for the fate of Intel, AMD can't strangle them as it basically can't produce enough processors. See this: https://www.statista.com/statistics/735904/worldwi...

No matter how and what it was counted, and how and what it wasn't, it's clear that AMD has a long way to go to strangle Intel - and, as AMD bounced from a low of 18%, the Intel of the future 5, or 10 years from now could too.

As for financial results, Intel can basically survive years without selling a single product - and, as a failing company, their financial situation is smiling - $77 billions revenue at a 55% gross margin.

So no, even failing as "hard" as they are now (which basically means just a bit of progress), they have at least a decade before falling into obsolescence.

(if the chip production crush abates and AMD can order twice as many chips as they do now, they'll have a real chance to turn the tables on Intel. However, that is purely an hypothetical at the moment, with Intel also competing on TSMC "top" products).

eSyr - Friday, January 14, 2022 - link

“AMD’s launch of Ryzen 3000 back in July 2019 was a first in bringing high performance x86 computing through the medium of chiplets.” — I think you're ignoring two-die Dual Core Pentium Ds (2005) and quad-core Penryns (2008).vlad42 - Friday, January 14, 2022 - link

The dual core Pentium Ds and quad core Penryns were composed of two whole Pentium D single cores processors and Penryn dual core processors, respectively, connected the same way 2P servers processors were connected. This is the same situation as the original Threadripper and Epyc processors. Each individual Pentium D single core chip and Penryn dual core chip were also sold as fully functional single core and dual core processors.Chiplets on the other hand, are generally understood to be chips that cannot function on their own. For example, a Zen 2 CPU chiplet, lacks the IO controllers needed to interface with the rest of the system.

mode_13h - Friday, January 14, 2022 - link

> This is the same situation as the original Threadripper and Epyc processors.That's sort of an unfair comparison, IMO. Those had integrated memory & PCIe controllers, whereas the former didn't.

vlad42 - Friday, January 14, 2022 - link

It is the same in the sense that any of these chips could be the only one in the processor package and everything would still work. If you had a processor with only a Zen 2/3 CPU chiplet or only the I/O chiplet, then it would not work. It does not matter if the memory controller or PCIe controller is integrated into something inside the processor package or on the motherboard chipset.If you are going to claim that the memory & PCIe/PCI/AGP controllers being on a motherboard chipset constitutes the processor being a chiplet, then everything that is not a true SOC is a chiplet. To me, this seems like a fairly ridiculous definition that fails to match how anyone actually uses the term.

mode_13h - Saturday, January 15, 2022 - link

> It does not matter if the memory controller or PCIe controller is integrated into> something inside the processor package or on the motherboard chipset.

It does because the topology is different, and that complicates the compute dies' interactions. In the prior examples, they only interacted for cache coherency. In the more recent examples, they have to route requests through either their own or the other's memory or PCIe controller. Further, the one they had to route it through might not even be directly connected.

> If you are going to claim that the memory & PCIe/PCI/AGP controllers being on a

> motherboard chipset constitutes the processor being a chiplet,

No, it's just simpler to implement multi-die, when your bus interface and memory controller is unified.

mode_13h - Friday, January 14, 2022 - link

> you're ignoring two-die Dual Core Pentium Ds (2005) and quad-core PenrynsThose used symmetrical chiplets. Maybe a trivial distinction... you decide.

FWIW, the first MCM I remember hitting the PC market was the Pentium Pro. Its L2 cache was on a separate die.