AMD Zen Architecture Roadmap: Zen 5 in 2024 With All-New Microarchitecture

by Ryan Smith on June 9, 2022 4:21 PM EST

Today is AMD’s Financial Analyst Day, the company’s semi-annual, analyst-focused gathering. While the primary purpose of the event is for AMD to reach out to investors, analysts, and others to demonstrate the performance of the company and why they should continue to invest in the company, FAD has also become AMD’s de-facto product roadmap event. After all, how can you wisely invest in AMD if you don’t know what’s coming next?

As a result, the half-day series of presentations is full of small nuggets of information about products and plans across the company. Everything here is high-level – don’t expect AMD to hand out the Zen 4 transistor floorplan – but it’s easily our best look at AMD’s product plans for the next couple of years.

Kicking off FAD 2022 with what’s always AMD’s most interesting update is the Zen architecture roadmap. The cornerstone of AMD’s recovery and resurgence into a competitive and capable player in the x86 processor space, the Zen architecture is the basis of everything from AMD’s smallest embedded CPUs to their largest enterprise chips. So what’s coming down the pipe over the next couple of years is a very big deal for AMD, and the industry as a whole.

Zen 4: Improving Performance and Perf-Per-Watt, Shipping Later This Year

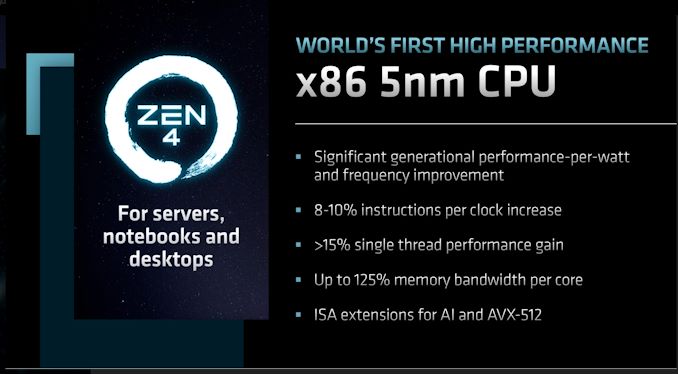

Diving right in, AMD is currently in the process of ramping up their Zen 4 architecture-based products. This includes the Ryzen 7000 (Raphael) client CPUs, as well as their 4th generation EPYC (Genoa) server CPUs. Both of these are due to launch later this year.

We’ve seen bits and pieces of information on Zen 4 thus far, most recently with the Ryzen 7000 announcement at Computex. Zen 4 brings new CPU core chiplets as well as a new I/O die, adding support for features such as PCI-Express 5.0 and DDR5 memory. And on the performance front, AMD is aiming for significant performance-per-watt and clockspeed improvements over their current Zen 3-based products.

Meanwhile, AMD is following up that Computex announcement by clarifying a few things. In particular, the company is addressing questions around Instruction per Clock (IPC) expectations, stating that they expect Zen 4 to offer an 8-10% IPC uplift over Zen 3. The initial Computex announcement and demo seemed to imply that most of AMD’s performance gains were from clockspeed improvements, so AMD is working to respond to that without showing too much of their hand months out from the product launches.

Coupled with that, AMD is also disclosing that they’re expecting an overall single-threaded performance gain of greater than 15% – with an emphasis on “greater than.” ST performance is a mix of IPC and clockspeeds, so at this point AMD can’t get overly specific since they haven’t locked down final clockspeeds. But as we’ve seen with their Computex demos, for lightly threaded workloads, 5.5GHz (or more) is currently on the table for Zen 4.

Finally, AMD is also confirming that there are ISA extensions for AI and AVX-512 coming for Zen 4. At this point the company isn’t clarifying whether either (or both) of those extensions will be in all Zen 4 products or just a subset – AVX-512 is a bit of a space and power hog, for example – but at a minimum, it’s reasonable to expect these to show up in Zen 4 server parts. The addition of AI instructions will help AMD keep up with Intel and other competitors in the short run, as CPU AI performance has already become a battleground for chipmakers. Though just what this does for AMD’s competitiveness there will depend in large part on just what instructions (and data types) get added.

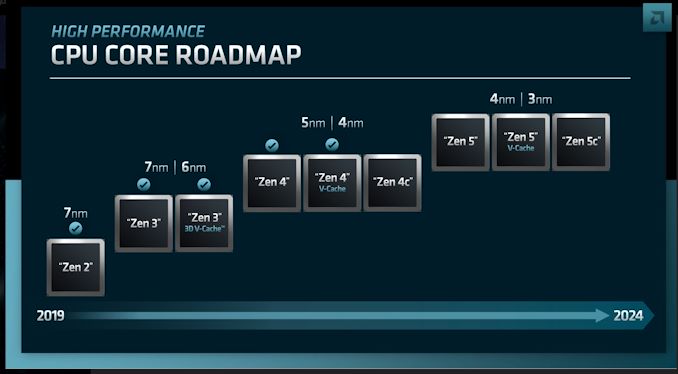

AMD will be producing three flavors of Zen 4 products. This includes the vanilla Zen 4 core, as well as the previously-announced Zen 4c core – a compact core that is for high density servers and will be going into the 128 core EPYC Bergamo processor. AMD is also confirming for the first time that there will be V-Cache equipped Zen 4 parts as well – which although new information, does not come as a surprise given the success of AMD’s V-Cache consumer and server parts.

Interestingly, AMD is planning on using both 5nm and 4nm processes for the Zen 4 family. We already know that Ryzen 7000 and Genoa are slated to use one of TSMC’s 5nm processes, and that Zen 4c chiplets are set to be built on the HPC version of N5. So it’s not immediately clear where 4nm fits into AMD’s roadmap, though we can’t rule out that AMD is playing a bit fast and loose with terminology here, since TSMC’s 4nm processes are an offshoot of 5nm (rather than a wholly new node) and are typically classified as 5nm variants to start with.

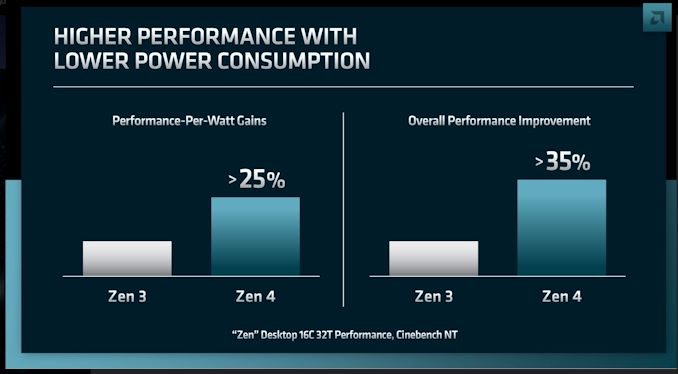

At this point, AMD is expecting to see a >25% increase in performance-per-watt with Zen 4 over Zen 3 (based on desktop 16C chips running CineBench). Meanwhile the overall performance improvement stands at >35%, no doubt taking advantage of both the greater performance of the architecture per-thread, and AMD’s previously disclosed higher TDPs (which are especially handy for uncorking more performance in MT workloads). And yes, these are terrible graphs.

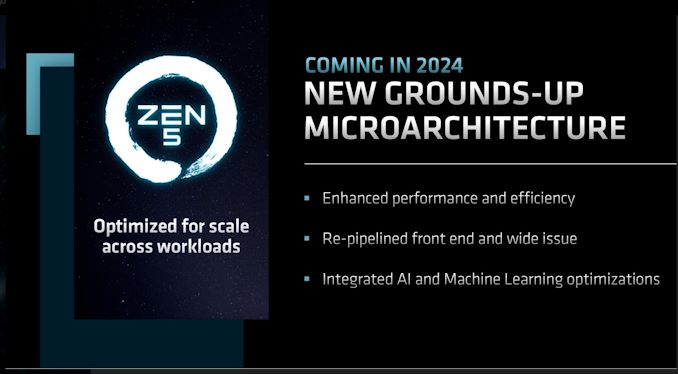

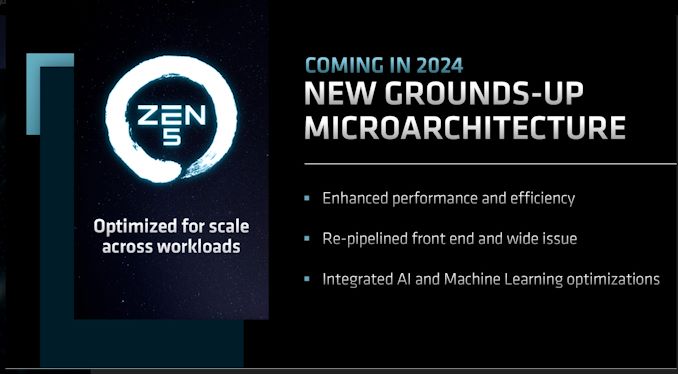

Zen 5 Architecture: All-New Microarchitecture for 2024

Meanwhile, carrying AMD’s Zen architecture roadmap into 2024 is the Zen 5 architecture, which is being announced today. Given that AMD isn’t yet shipping Zen 4, their details on Zen 5 are understandably at a very high level. None the less, they also indicate that AMD won’t be resting on their laurels, and have some aggressive updates planned.

The big news here is that AMD is terming the Zen 5 architecture as an “All-new microarchitecture”. Which is to say, it’s not merely going to be an incremental improvement over Zen 4.

In practice, no major vendor designs a CPU architecture completely from scratch – there’s always going to be something good enough for reuse – but the message from AMD is clear: they’re going to be doing some significant reworking of their core CPU architecture in order to further improve their performance as well as energy efficiency.

As for what AMD will disclose for right now, Zen 5 will be re-pipelining the front end and once again increasing their issue width. The devil is in the details here, but coming from Zen 3 and its 4 instruction/cycle decode rate, it’s easy to see why AMD would want to focus on that next – especially when on the backend, the integer units already have a 10-wide issue width.

Meanwhile, on top of Zen 4’s new AI instructions, Zen 5 is integrating further AI and machine learning optimizations. AMD isn’t saying much else here, but they have a significant library of tools to pick from, covering everything from AI-focused instructions to adding support for even more data types.

AMD expects the Zen 5 chip stack to be similar to Zen 4 – which is to say that they’re going to have the same trio of designs: a vanilla Zen 5 core, a compact core (Zen 5c), and a V-Cache enabled core. For AMD’s customers this kind of continuity is very important, as it gives customers a guarantee that AMD’s more bespoke configurations (Zen 4c & V-Cache) will have successors in the 2024+ timeframe. From a technical perspective none of this is too surprising, but from a business standpoint, customers want to make sure they aren’t adopting dead-end hardware.

Finally, AMD has an interesting manufacturing mix planned for Zen 5. Zen 5 CPU cores will be fabbed on a mix of 4nm and 3nm processes, which unlike the 5nm/4nm mix for Zen 4, TSMC’s 4nm and 3nm nodes are very different. 4nm is an optimized version of 5nm, whereas 3nm is a whole new node. So if AMD’s manufacturing plans move ahead as currently laid out, Zen 5 will be straddling a major node jump. That said, it’s not unreasonable to suspect that AMD is hedging their bets here and leaving 4nm on the table in case 3nm isn’t as far along as they’d like.

Wrapping things up, the Zen 5 architecture is slated for 2024. AMD isn’t giving any further information on when in the year that might be, though looking at Zen 3 and Zen 4, both of those were/will be released later on in 2020 and 2022 respectively. So H2/EOY 2024 is as good as guess as any.

156 Comments

View All Comments

michael2k - Sunday, June 12, 2022 - link

Fundamentally it’s for performance.There are always going to be time insensitive or low performance tasks like file copying, network operations, and UI handling. If you can allocate those tasks to a 10W core instead of a 30W core you get an additional 20W, of both heat and energy, you can spend on a 30W core.

In other words if your system throttles after 3 seconds at max performance, that extra 20W budget may increase the time your 30W cores can run at full throttle for an additional 4 seconds. Or maybe it can run at 4/5 performance without ever throttling.

Khanan - Friday, June 10, 2022 - link

No thanks. That shit will hopefully not be needed with AMD.michael2k - Sunday, June 12, 2022 - link

I imagine they will, and due to their chiplet design it shouldn’t have any extra complexity. They can allocate low resource tasks to efficiency cores and allocate the extra watts saved towards the performance cores.mode_13h - Sunday, June 12, 2022 - link

Well, if they were, then you'd expect they would've announced an efficiency core by now.As it stands, their answer to Intel's E-cores is the Zen 4c, and we have yet to see how its efficiency really compares to the normal Zen 4. It might not be a big enough gap to justify having a Big.Little configuration.

michael2k - Sunday, June 12, 2022 - link

If we assume the 4C is their efficiency core we can compare their announced products. Their performance core maxes out at 96 cores in a pin compatible part vs 128 efficiency cores. The assumption is that if both parts consume the same amount of energy then their e cores consume 3/4 the energy and emit 3/4 the heat of their p cores.If they further downclock the e cores slightly, they will then consume half, possibly even a third, of the energy.

So if they have a 1:7 e/p ratio we could end up with 12e/84p; because the e cores would be running OS tasks, networking and file copies and other time insensitive tasks, the energy previously wasted by running them on a p core can instead be allocated to one of the existing p cores. It’s possible those 84 p cores don’t throttle any more compared to a 96 p core part if there is enough surplus energy budget.

mode_13h - Monday, June 13, 2022 - link

> If they further downclock the e cores slightly, they will then consume half,> possibly even a third, of the energy.

That downclocking should apply equally to the regular Zen 4 cores. So, we're back to your original figure of 3/4th the power, and we don't know how much they'd have *already* been downclocked, just to hit that target! So, 3/4ths is probably more of a best-case estimate than a starting point.

Khanan - Monday, June 13, 2022 - link

Then you’re wrong. Big little is a old design, if AMD wanted it they would’ve announced or made something at this point but they didn’t. They have also publicly said that they are not planning to do so, because they don’t need it, their Regular cores are efficient enough and not bloated like Intels. Modern tech not outdated 1637361th gen core arch.Otritus - Thursday, June 9, 2022 - link

Based on history, AMD’s APUs using their architectures are always slightly more advanced and delayed than their desktop counterparts. From this I gather that the Zen 4 APUs will likely be on 4nm. Zen 5 is likely on both nodes, either because TSMC N3 is facing delays or because the APUs will be a ‘tick’ on 3nm with the CPUs a ‘tock’ on 4nm.Silver5urfer - Thursday, June 9, 2022 - link

AMD is now showing the muscle. No question.Their map is so solid now, Intel on the other hand is bragging about Foveros and other things. And on the consumer side more of that Biglittle junk because they cannot fix Core uArch to scale past 8P anymore. Anyways Zen 4, 5 with V-Cache was not surprising but Genoa-X 1GB L3 was because I didn't expect them to reveal it before even Genoa launched.

No more big.little bs rumors, AMD is using 4c for Bergamo as we all know 5c will also have similar successor. Because ARM's Neoverse V1 and N2 are coming with high density cores. AMD want's to cull them before itself, good move. x86 needs to reign this space and consumer space else the insane BS fragmentation and software issues with compat will show up. And AMD doesn't need to break the CPUs as they provide full high performance x86 cores without the added "efficiency" baggage on a Desktop. Intel is meanwhile stuck until they find a replacement for the Core series uArch.

At this point not sure if their AM5 socket with 1718 pins will stick until 2024. I hope they do, that would make Intel pathetic given how they are going to axe LGA1700 / 1800 pins total for a new LGA1851 socket ripping off people again like LGA1511 disasters. Shame when ILM is busted on Alder Lake.

For consumer Zen 4 Raphael / Ryzen 7000, I'm waiting to see how the clocks will stay now. Also most importantly their IMC and Firmware. The IOD is now TSMC 6nm, hopefully all the dreaded garbage WHEA and USB nonsense is gone. Also AGESA 1.2.0.7 has it's share of issues apparently despite aiming to fix TPM and stutters. This is the main weakness of AMD, garbage firmware and poor tuning experience. CO is very much head ache given how the clock behavior is on AMD and the heat on Zen 3 scales heavily dependent on that unlike Intel which can stick to a given clock and poor IMC with annoying XMP issues vs Intel again.

lemurbutton - Friday, June 10, 2022 - link

LOL @ this AMD fanboy.Who cares about AMD vs Intel anymore? Wake up. M series is destroying both. I doubt AMD can catch up to the M1 until Zen6. By then, M5 will be out since Apple will do a yearly update.