Silicon Motion SM2256 SSD Controller Preview: TLC for Everyone

by Kristian Vättö on June 17, 2015 8:15 AM EST- Posted in

- Storage

- SSDs

- TLC

- Silicon Motion

- SM2256

The SSD industry has been talking about TLC NAND for over three years now. We published our first post, Understanding TLC NAND, back in early 2012, but in three years we have actually seen very little TLC NAND making it to the SSD market. Samsung was an early adopter by introducing the SSD 840 in September 2012, but Samsung has always been a special case as its SSD business is fully vertically integrated. When you design and manufacture everything in-house, it's obvious that you will have a technological advantage when it comes to adopting new technologies.

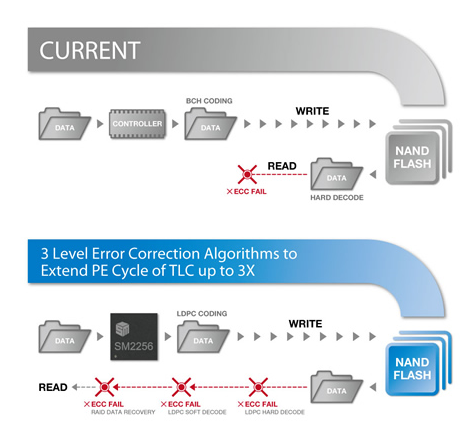

TLC is tightly linked with both controller technology and NAND production because TLC inherently has a higher error rate, which needs a stronger controller (although admittedly Samsung has had some issues with TLC). The lack of proper controller is the reason why other NAND vendors haven't invested as heavily on TLC as Samsung because Micron, SanDisk and the like have to rely on whatever third party controllers are available on the market. Without a high volume product to put your TLC NAND into, it means that there's no reason to produce TLC in a large scale, which defeats the cost savings that TLC bring. Micron tried to promote its 25nm TLC NAND for a while a few years ago, but it quickly realized that the available SSD controllers aren't capable of creating a reliable product -- at least not one that would bring any cost savings since the drive would need serious over-provisioning for endurance and ECC parity.

Due to the lack of controller support, nobody other than Samsung and SanDisk have a TLC SSD on the market, although SanDisk had to rely on heavy over-provisioning with 5:1 parity ratio since the Marvell controller used in the Ultra II wasn't designed with TLC in mind. Silicon Motion's SM2256 will be the first commercially available controller and firmware combo with TLC support and today we are taking an early look of the platform in the form of a reference design sample. ADATA already announced its SP550 SSD that will be based on the new SM2256 controller and available later in the summer, but given how many OEMs rely on Silicon Motion's controllers nowadays we will likely see a large number of SM2256 based TLC drives entering the market by the end of the year.

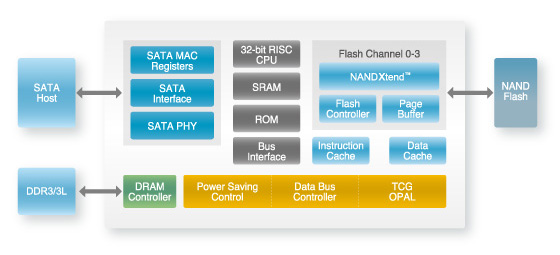

Architecturally the SM2256 shares the same core design as its predecessor SM2246EN. The design is modular, which allows Silicon Motion to change parts of the controller without redoing the rest. It features the same single 32-bit Argonaut RISC processor core as the SM2246EN, which is quite unique because we have seen many SSD controller vendors moving towards multi-core ARM architectures. A single custom core obviously brings efficiency gains and we've witnessed those in the SM2246EN, but the downside of such limited CPU power is sustained performance when the controller has to perform garbage collection at the same time as processing host IOs.

The only dramatic change is in the error correction circuitry as the SM2256 supports Low Density Parity Check (LDPC) error correction codes instead of more common and less powerful BCH ECC. Silicon Motion calls its ECC technology as NANDXtend, and it's a combination of LDPC hard and soft decode along with RAID5-like data recovery. The benefit of having three levels of ECC is performance because LDPC soft decode and recovery from parity both have a relatively noticeable impact on performance and are typically only needed when the drive approaches its end of life (i.e. when the NAND has been cycled a lot). Uncycled NAND has much higher reliability because the tunnel oxide hasn't worn out due to P/E cycles, so only very little ECC is needed and LDPC hard decode is sufficient and also doesn't have a dramatic impact on performance.

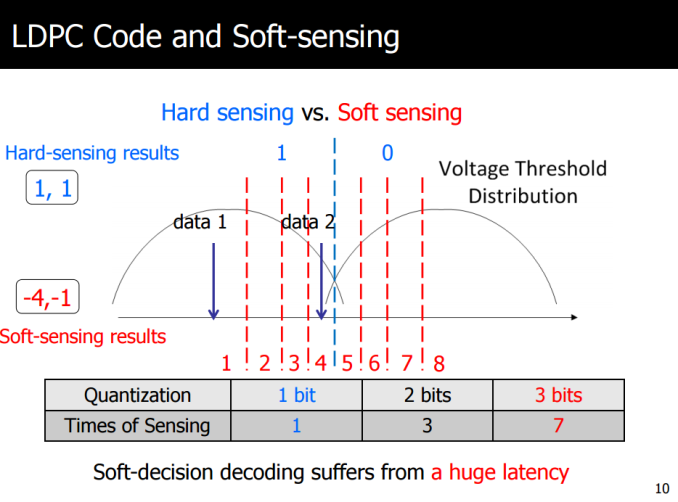

Source: usenix

The reason why hard decode is faster than soft decode lies in how the voltage of a cell is sensed. Hard sensing is binary based, so for an SLC cell like in the graph above the cell can be either 1 or 0. However, as you can see, the voltage threshold distributions overlap slightly and that's actually far worse with MLC and TLC since there are more voltage states. In soft sensing the voltage distributions are divided into several segments, which requires more precision and iterations. For example in segment 4 the bit value can be either 1 or 0 as the distributions overlap, so probability algorithms are used to figure out the correct value. To be honest, ECC codes and the way they work are way over my head, but in case you are familiar with ECC and want to learn more, I suggest you simply google LDPC as there are numerous publicly available academic papers that go into more depth about this topic.

Silicon Motion claims that its NANDXtend technology can extend the endurance of TLC NAND by up to three times, making TLC more robust for heavier workloads and also allowing the use of lower quality NAND that some OEMs may use anyway due to the lack of in-house binning equipment. Unfortunately I didn't have any time to do extended endurance testing with the SM2256 yet to validate Silicon Motion's claims, but I will be sure to test that once we have a retail drive on our hands,

| Silicon Motion SM2256 Specifications | |

| Host Interface | SATA 6Gbps |

| NAND Interface | ONFi 3.0, Toggle 2.0 & asynchronous |

| # of NAND Channels | 4 |

| CE per Channel | 8 |

| Sequential Read | 524MB/s |

| Sequential Write | 400MB/s |

| 4KB Random Read | 90K IOPS |

| 4KB Random Write | 70K IOPS |

| Encryption | AES-256 & TCG Opal 2.0 |

The SM2256 has eight chip enablers (CE) per channel, meaning that it can simultaneously talk to up to 32 NAND dies, but one CE can control more than one die, resulting in capacities of up to 2TB with one CE per four dies.

The engineering sample Silicon Motion sent us uses Samsung's 19nm 128Gbit TLC NAND, which is the same NAND that is found inside the 840 EVO. Samsung doesn't sell its TLC NAND to others in high volume, so we likely won't see this configuration on the market at all. The SM2256 does, of course, support TLC NAND from all other vendors as well (even Toshiba's 15nm).

Like all TLC SSD designs we have seen, Silicon Motion employs SLC caching in the SM2256 to improve performance and endurance. The size of the SLC cache is configurable by the OEM, but generally the cache size is between 3GB and 12GB depending on the capacity of the drive. The OEM can also configurate whether all IOs are cached or just smaller ones (e.g. 16KB and below), but the early stock firmware that our sample shipped with caches all IOs regardless of the size.

| AnandTech 2015 SSD Test System | |

| CPU | Intel Core i7-4770K running at 3.5GHz (Turbo & EIST enabled, C-states disabled) |

| Motherboard | ASUS Z97 Deluxe (BIOS 2205) |

| Chipset | Intel Z97 |

| Chipset Drivers | Intel 10.0.24+ Intel RST 13.2.4.1000 |

| Memory | Corsair Vengeance DDR3-1866 2x8GB (9-10-9-27 2T) |

| Graphics | Intel HD Graphics 4600 |

| Graphics Drivers | 15.33.8.64.3345 |

| Desktop Resolution | 1920 x 1080 |

| OS | Windows 8.1 x64 |

- Thanks to Intel for the Core i7-4770K CPU

- Thanks to ASUS for the Z97 Deluxe motherboard

- Thanks to Corsair for the Vengeance 16GB DDR3-1866 DRAM kit, RM750 power supply, Hydro H60 CPU cooler and Carbide 330R case

34 Comments

View All Comments

Oxford Guy - Saturday, June 20, 2015 - link

Apple reportedly abandoned TLC because of the defects.serndipity - Saturday, June 20, 2015 - link

Have noticed that, as the NAND manufacturers shrunk the die process, issues with both MLC and TLC based SSDs have begun surfacing.Glad to see that Samsung, with its 3D NAND technology, used in the 850 PRO and 850 EVO, has been able to return to a much more stable process size (e.g. almost 3X that of current MLC).

viktorp - Thursday, July 2, 2015 - link

TLC NAND isn’t welcome at any price.Ask yourself simple question – what parts of your personal data will you trust to storage designed specifically to have 10 times less endurance than technology it is supposed to replace (MLC).

I am upset just thinking that someone thought of it as being a good idea.

cbjwthwm - Thursday, September 3, 2015 - link

The big problem here is a newer gen product at 2x the capacity of the equivalent architecture Sandisk Ultra II which for the most part gets outperformed by it. It would be interesting to see what the shipping firmware of this type of product eventually performed like compared to the reference design, but otherwise I see no reason to consider this vs the Marvell-based Ultra II.