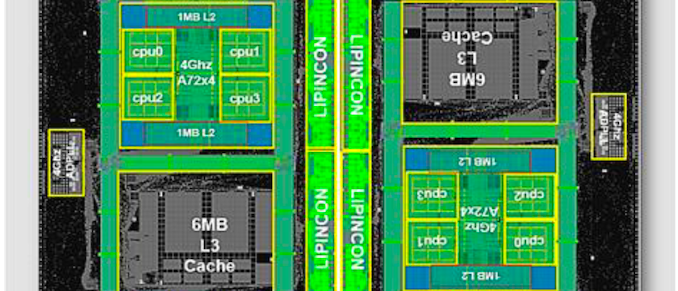

LIPINCON

Arm and TSMC this week unveiled their jointly developed proof-of-concept chip that combines two quad-core Cortex-72-based 7 nm chiplets on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) interposer. The two chips are connected using the company’s Low-voltage-IN-Package-INterCONnect (LIPINCON) interface. The chip is meant to showcase potential of Arm’s and TSMC’s technologies for high-performance computing applications. Large SoCs are hard and expensive to manufacture with decent yields using leading-edge process technologies these days. In fact, many elements of these SoCs do not need to be produced using the latest nodes at all. As a result, many chipmakers turn to the so-called chiplet design approach that relies on multiple smaller dies optimized for a particular function and produced using an appropriate process technology. Smaller dies afford better yields and better binning...