Samsung to Use SiFive RISC-V Cores for SoCs, Automotive, 5G Applications

by Anton Shilov on December 12, 2019 11:00 AM EST

At the annual RISC-V Summit this week, Samsung disclosed the use SiFive’s RISC-V cores for upcoming chips for a variety of applications. The company is joining a growing list of leading high-tech companies that have adopted the RISC-V architecture.

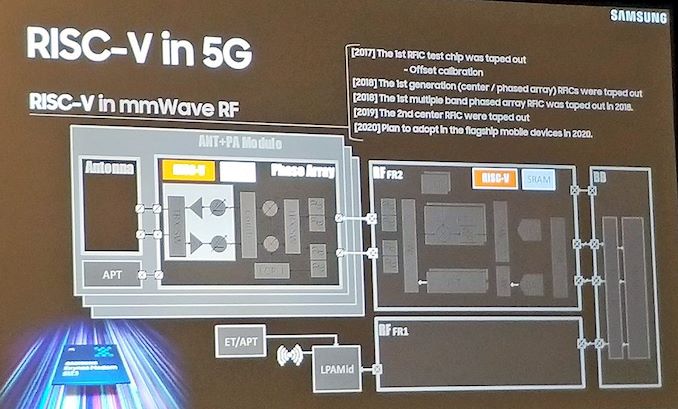

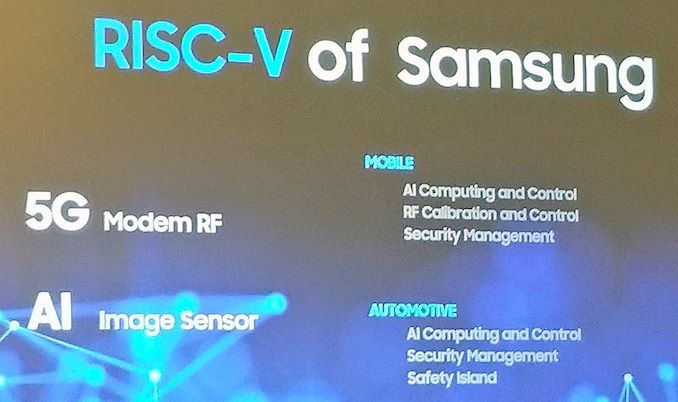

One of the applications that Samsung is using RISC-V cores in is mmWave RF processing by its upcoming 5G RF front-end modules. The latter will be used for Samsung’s flagship 5G smartphones due in 2020. The RISC-V cores will also be used for AI image sensors, security management, AI computing & control.

It is noteworthy that Samsung taped out its first chip with a RISC-V core(s) as early as in 2017, so it started to work on it even earlier. In three years, Samsung has iterated on its designs and is now planning to adopt RISC-V cores for commercial applications, starting from mmWave RF processing in mobiles and expanding beyond them.

Besides the announcement of the RISC-V core integration, it's also Samsung's first instance of them talking about their mmWave modules in public. Unlike Qualcomm, Samsung tends to remain quiet about their developments until it's nearing commercialisation, and even then in a lot of cases we don't know too much about their designs. Nevertheless, it looks like the company has had mmWave designs for some time.

Samsung will be the fourth major company that has publicly disclosed its plans to adopt the open-source RISC-V architecture after Western Digital, NVIDIA, and Qualcomm. Western Digital intends to use the technology for a variety of applications, including SSD and HDD controllers. NVIDIA reportedly plans to use it for GPU memory controllers, whereas Qualcomm is set to use RISC-V for mobile SoCs.

All of the said companies have historically used processing cores based on architectures developed by Arm, and will likely continue to use them in the foreseeable future alongside RISC-V implementations. The advantage of RISC-V and the rationale for the vendors like Samsung choosing SiFive designs over Arm designs might be financial, as the former is likely undercutting its big competitor in price. For vendors doing their own microarchitecture designs, such as WD, RISC-V comes with no royalties attached, and offered more flexibility for vendors in terms of implementation. Arm only recently changed course in allowing vendor to implement their own custom instructions to the Cortex designs and architecture. Custom instructions developed by SoC vendors might be a huge benefit for efficient handling of ECC and RF processing among other things.

Related Reading:

- SiFive Announces First RISC-V OoO CPU Core: The U8-Series Processor IP

- Western Digital’s RISC-V "SweRV" Core Design Released For Free

- Western Digital Reveals SweRV RISC-V Core, Cache Coherency over Ethernet Initiative

- Western Digital to Use RISC-V for Controllers, Processors, Purpose-Built Platforms

Sources: The Register, Chris Williams/Twitter

18 Comments

View All Comments

MASSAMKULABOX - Thursday, December 12, 2019 - link

SO we await the first implementation of boh Android on Rv or Windows on Rv. possibly even low level dup of X86 .. not sure where it has advantages besides cost and royalty-free tho. And obscurity.prisonerX - Thursday, December 12, 2019 - link

RISC-V is clean, efficient, robust and extensible. It's open and free (as in freedom) and encourages collaboration. The fact that it's royalty-free is almost irrelevant since most of the expense of a new processor is in the chip design.The point is that there is a fast growing ecosystem of companies offering various designs and services for RISC-V which makes developing a new chip less risky and less financially onerous.

bji - Thursday, December 12, 2019 - link

I work in software and everyone always thinks that any new implementation is 'clean, efficient, robust, and extensible' ... things always look that way until all of the use cases which the old software supported that the new software just ignored or glossed over have to be implemented, after which the new shiny implementation is nearly as bad as the old one was.The moral of this story is not that rewrites are bad, but the over optimistic belief that the first re-implementation represents how much 'cleaner' the software could have been is usually an illusion. It wil get ugly again fast.

I read the entire RISC-V architecture doc. I am not a hardware engineer so alot of it I could only generalize the meanings and extract some of the details. But some of their choices do seem odd. They are significantly restrictive on how far you can branch in a single instruction. There were other oddities, I don't recall them all.

Some other poster here commented on quite a few good ones in the last RISC-V article. Hopefully he/she can repeat that because I'd like to see those points further discussed.

michael2k - Thursday, December 12, 2019 - link

I imagine some of the attraction is that you aren't paying a license fee, architecture fee, and then per chip royalty with RISC-V compared to ARM. With RISC-V, as I understand it, there is a free version and a licensed version, which means you can play with the SiFive implementation at zero cost and pay for the licensed version if you prefer as well.I don't know that their decisions wrt branch/jump are a big deal, though it is strange that they limit jumps to unconditional 12 bit offset or conditional 20 bit offset

bji - Thursday, December 12, 2019 - link

I agree with everything you said. But I was responding to prisonerX's statement about the design being "clean, efficient, robust, and extensible". From my reading it seems kind of simplistic, which can be confused for 'clean, efficient, and robust'. I am very interested in learning from more those more educated on chip and ISA design whether or not my conclusions are valid.FunBunny2 - Thursday, December 12, 2019 - link

'clean, efficient, robust, and extensible'well... *nix/C have proved over the decades that this can, in fact, be true. whether any given application makes more sense in RISC or CISC is a separate question. compiler writers, from what I've read, hate RISC since implementing a robust C compiler is a pain. there's a reason that COBOL hasn't been fun on RISC. and, of course, it's widely reported that the real hardware in X86 machines is a RISC machine.

ksec - Thursday, December 12, 2019 - link

Like bji have said, there is nothing "Clean, efficient, Robust and extensible" about RISC-V than say ARMv8. And some CPU veteran might even argue RSIC-V are making some questionable choices in their ISA.And royalty free is relevant because of its usage for now, and likely foreseeable future are in embedded application.

WPX00 - Saturday, December 14, 2019 - link

also risc-v was developed here in berkeley... and as a berkeley alum it'd be awesome to see it take off. selfish i know.brucehoult - Thursday, December 12, 2019 - link

It will be several more years before RISC-V is able to replace ARM as the main application processor cores in a high end mobile device. The U84 core SiFive announced in October is comparable to the A72 in the Raspberry Pi 4 now, or in high end phones three years ago. RISC-V is catching up, but ARM also continues to move forward. The things Samsung is planning to use RISC-V for at the moment are in peripherals such as the radio baseband or the camera, not the main processor running Android and apps.Kangal - Friday, December 13, 2019 - link

I would say they're still behind the ARM Cortex A72/73.And I doubt they can catch-up with the deployment of the Cortex A77, and possibly a small successor to that in the Cortex A78. Meanwhile, they're actually forgo ARMv8.2 and pushing forward on a "start fresh" with the development of ARMv9 for 2022.

So can RISC-V catch-up by 2022... I doubt it.

But I hope they do, in fact, I hope they surpass ARM. I also hope an open-sourced ecosystem emerges to bring a competitive Linux to the mainstream. The current Android-ARM is actually quite proprietary, maybe not as much as Windows-x86 but I digress.