TSMC

Taiwan Semiconductor Manufacturing Co. this week said its revenue for the second quarter 2024 reached $20.82 billion, making it the company's best quarter (at least in dollars) to date. TSMC's high-performance computing (HPC) platform revenue share exceeded 52% for the first time in many years due to demand for AI processors and rebound of the PC market. TSMC earned $20.82 billion USD in revenue for the second quarter of 2024, a 32.8% year-over-year increase and a 10.3% increase from the previous quarter. Perhaps more remarkable, $20.82 billion is a higher result than the company posted Q3 2022 ($20.23 billion), the foundry's best quarter to date. Otherwise, in terms of profitability, TSMC booked $7.59 billion in net income for the quarter, for a gross margin of...

Ampere’s Product List: 80 Cores, up to 3.3 GHz at 250 W; 128 Core in Q4

With the advent of higher performance Arm based cloud computing, a lot of focus is being put on what the various competitors can do in this space. We’ve covered...

19 by Dr. Ian Cutress on 6/23/2020New #1 Supercomputer: Fugaku in Japan, with A64FX, take Arm to the Top with 415 PetaFLOPs

High performance computing is now at a point in its existence where to be the number one, you need very powerful, very efficient hardware, lots of it, and lots...

46 by Dr. Ian Cutress on 6/22/2020Russia’s Elbrus 8CB Microarchitecture: 8-core VLIW on TSMC 28nm

All of the world’s major superpowers have a vested interest in building their own custom silicon processors. The vital ingredient to this allows the superpower to wean itself off...

93 by Dr. Ian Cutress on 6/1/2020TSMC To Build 5nm Fab In Arizona, Set To Come Online In 2024

In a big shift to their manufacturing operations – and a big political win domestically – TSMC has announced that the company will be building a new, high-end fab...

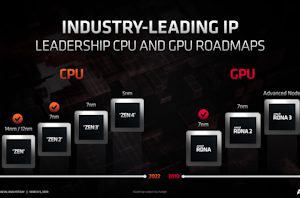

100 by Ryan Smith on 5/15/2020AMD Clarifies Comments on 7nm / 7nm+ for Future Products: EUV Not Specified

As part of AMD’s Financial Analyst Day 2020, the company gave the latest updates for its CPU and GPU roadmap. A lot of this we have seen before, with...

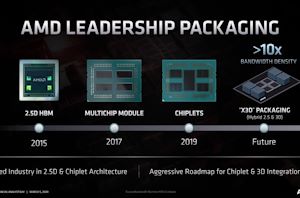

37 by Dr. Ian Cutress on 3/5/2020AMD Discusses ‘X3D’ Die Stacking and Packaging for Future Products: Hybrid 2.5D and 3D

One of AMD’s key messages at its Financial Analyst Day 2020 is that the company wants to remain on the leading edge when it comes to process node technology...

12 by Dr. Ian Cutress on 3/5/2020TSMC & Broadcom Develop 1,700 mm2 CoWoS Interposer: 2X Larger Than Reticles

With transistor shrinks slowing and demand for HPC gear growing, as of late there has been an increased interest in chip solutions larger than the reticle size of a...

18 by Anton Shilov on 3/4/2020TSMC Boosts CapEx by $1 Billion, Expects N5 Node to Be Major Success

TSMC is on track to begin high-volume production of chips using its 5 nm technology in the coming months, the company said in its conference call last week. While...

40 by Anton Shilov on 1/22/2020An Interview with AMD’s CTO Mark Papermaster: ‘There’s More Room At The Top’

On the back of a very busy 2019, AMD is gaining market share and is now a performance leader in a lot of CPU segments. The company has executed...

68 by Dr. Ian Cutress on 12/30/2019Early TSMC 5nm Test Chip Yields 80%, HVM Coming in H1 2020

Today at the IEEE IEDM Conference, TSMC is presenting a paper giving an overview of the initial results it has achieved on its 5nm process. This process is going...

64 by Dr. Ian Cutress on 12/11/2019AMD Q4: 16-core Ryzen 9 3950X, Threadripper Up To 32-Core 3970X, Coming November 25th

AMD is set to close out the year on a high note. As promised, the company will be delivering its latest 16-core Ryzen 9 3950X processor, built with two...

171 by Dr. Ian Cutress on 11/7/2019GlobalFoundries and TSMC Sign Broad Cross-Licensing Agreement, Dismiss Lawsuits

GlobalFoundries and TSMC have announced this afternoon that they have signed a broad cross-licensing agreement, ending all of their ongoing legal disputes. Under the terms of the deal, the...

27 by Anton Shilov on 10/28/2019TSMC: 5nm on Track for Q2 2020 HVM, Will Ramp Faster Than 7nm

TSMC’s 5 nm (N5) manufacturing technology is projected to provide significant benefits when it comes to performance, power, and area scaling, which is why the contract maker of semiconductors...

27 by Anton Shilov on 10/23/2019TSMC Radically Boosts CapEx to Expand Production Capacities, To Reach $14B For 2019

Forecasting strong demand for its 5 nm and 7 nm class process technologies in the coming years, TSMC has announced that it's increasing its capital expenditure for 2019 by...

18 by Anton Shilov on 10/18/2019Samsung & TSMC Develop 8nm & 7nm Automotive-Grade Nodes

As vehicles are getting ‘smarter’ and gaining autopilot capabilities, it is easy to predict that the demand for higher-performing and more complex automotive SoCs will be growing rapidly in...

29 by Anton Shilov on 10/14/2019TSMC: N7+ EUV Process Technology in High Volume, 6nm (N6) Coming Soon

TSMC announced on Monday that its customers have started shipping products based on chips made by TSMC using its N7+ (2nd Generation 7 nm with EUV) process technology that...

27 by Anton Shilov on 10/8/2019TSMC Counter-sues GlobalFoundries: Accuses US Fab of Infringing Patents Across Numerous Process Nodes

In a not-unexpected move, TSMC late on Monday filed a lawsuit against GlobalFoundries, its pure-play foundry rival, accusing the manufacturer of patent infringment. In the suit, a response to...

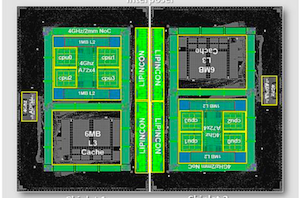

24 by Anton Shilov on 10/1/2019Arm & TSMC Showcase 7nm Chiplet, Eight A72 at 4GHz on CoWoS Interposer

Arm and TSMC this week unveiled their jointly developed proof-of-concept chip that combines two quad-core Cortex-72-based 7 nm chiplets on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) interposer. The two chips are connected...

26 by Anton Shilov on 9/27/2019TSMC Responds to Lawsuit by GlobalFoundries: Allegations Are Baseless

TSMC has responded to GlobalFoundries accusations of patents infringements. The world’s largest foundry said that it would defend itself in courts and that it considered allegations as baseless. The...

62 by Anton Shilov on 8/27/2019GlobalFoundries Sues TSMC Over Patent Infringement; Apple, Qualcomm, Others Named Defendants

GlobalFoundries has filed a lawsuit against TSMC and its clients in the USA and Germany alleging the world’s largest contract maker of semiconductors of infringing 16 of its patents...

97 by Anton Shilov on 8/26/2019